**Universidade Federal da Bahia

Escola Politécnica

Programa de Pós-Graduação em

Engenharia Elétrica**

Arnaldo Oliveira Cunha Junior

**Inversor Fotovoltaico Monofásico sem

Transformador com Atenuação de Corrente de

Fuga**

Salvador-Ba – Brasil

Julho de 2023

Arnaldo Oliveira Cunha Junior

**Inversor Fotovoltaico Monofásico sem Transformador com

Atenuação de Corrente de Fuga**

Dissertação submetida ao Programa de Pós-Graduação em Engenharia Elétrica da Universidade Federal da Bahia como parte dos requisitos necessários para obtenção do grau de Mestre em Engenharia Elétrica.

Orientador: Filipe Antônio da Costa Bahia, DSc., UFBA

Coorientador: João Paulo Ramos Agra Méllo, DSc., UFRPE

Salvador-Ba – Brasil

Julho de 2023

Ficha catalográfica elaborada pela Biblioteca Bernadete

Sinay Neves, Escola Politécnica – UFBA.

---

C972 Cunha Junior, Arnaldo Oliveira.

Inversor fotovoltaico monofásico sem transformador com atenuação de corrente de fuga / Arnaldo Oliveira Cunha Junior. – Salvador, 2023.

124f.: il.

Orientador: Prof. Dr. Filipe Antônio da Costa Bahia.

Coorientador: Prof. Dr. João Paulo Ramos Agra Méllo.

Dissertação (mestrado) – Programa de Pós-Graduação em Engenharia Elétrica, Escola Politécnica, Universidade Federal da Bahia, 2023.

1. Sistemas fotovoltaicos. 2. Transformador. 3. Inversor monofásico. 4. Corrente de fuga. I. Bahia, Filipe Antônio da Costa. II. Méllo, João Paulo Ramos Agra. III. Universidade Federal da Bahia. IV. Título.

CDD: 621.314

---

Arnaldo Oliveira Cunha Junior

## Inversor Fotovoltaico Monofásico sem Transformador com Atenuação de Corrente de Fuga

Dissertação submetida ao Programa de Pós-Graduação em Engenharia Elétrica da Universidade Federal da Bahia como parte dos requisitos necessários para obtenção do grau de Mestre em Engenharia Elétrica.

Trabalho aprovado. Salvador-Ba – Brasil, 21 de julho de 2023:

Documento assinado digitalmente

FILIPE ANTONIO DA COSTA BAHIA

Data: 04/09/2025 14:19:54-0300

Verifique em <https://validar.iti.gov.br>

---

Orientador: Filipe Antônio da Costa Bahia,

DSc., UFBA

Documento assinado digitalmente

JOAO PAULO RAMOS AGRA MELLO

Data: 03/09/2025 17:33:41-0300

Verifique em <https://validar.iti.gov.br>

---

Coorientador: João Paulo Ramos Agra Méllo,

DSc., UFRPE

---

Nayara Brandão de Freitas, DSc., INESC TEC

Documento assinado digitalmente

NADY ROCHA

Data: 03/09/2025 17:17:03-0300

Verifique em <https://validar.iti.gov.br>

---

Nady Rocha, DSc., UFPB

Documento assinado digitalmente

MAICON DEVID PEREIRA

Data: 03/09/2025 20:01:30-0300

Verifique em <https://validar.iti.gov.br>

---

Maicon Deivid Pereira, DSc., UFBA

Salvador-Ba – Brasil

Julho de 2023

*Este trabalho é dedicado à minha família.*

# Agradecimentos

Primeiramente agradeço a Deus por todas as oportunidades e desafios encontrados.

Agradeço à minha mãe Elenilde e meu pai Arnaldo pelo amor e suporte incondicional.

À minha irmã Andreia pelo amor e conselhos tão valiosos.

Ao professor Filipe pela disponibilidade, confiança, apoio e conhecimento passado ao longo do trabalho.

Ao professor João Paulo pela experiência e conhecimento compartilhados durante o desenvolvimento do trabalho.

Aos amigos de laboratório Luan, Diego, Alan, Michael, Edemar, Romário e Leandro pelos bons momentos e pela parceria diária.

Aos meus amigos que tornam todos os momentos muito mais leves. Em especial: Adriana, Naiara, Isaura, Letícia, Isabella, Paulo, Ildemar, Caio, Matheus e Yuri.

*“Tudo tem o seu tempo determinado,

e há tempo para todo o propósito debaixo do céu.”*

*(Eclesiastes 3:1)*

# Resumo

Este trabalho apresenta uma nova topologia de inversor fotovoltaico sem transformador para sistemas fotovoltaicos. O principal desafio enfrentado nos sistemas sem transformador é a corrente de fuga que circula através das capacitâncias parasitas dos painéis fotovoltaicos. Para reduzir essa corrente, é necessário garantir que a tensão de modo comum não apresente oscilações de alta frequência. As topologias de inversores que reduzem a corrente de fuga podem ser divididas em três grandes grupos: inversores com terra comum, com desacoplamento do estado-zero e inversores com grampeamento ao ponto central do barramento de corrente contínua (**CC**). Neste trabalho, é proposto um inversor com desacoplamento no lado de corrente alternada (**CA**) do inversor e grampeamento ao ponto central do barramento **CC**. Além da redução da corrente de fuga, o inversor apresenta alta eficiência em comparação às topologias de inversor sem transformador já existentes na literatura. No decorrer do trabalho, realiza-se uma vasta revisão das topologias de inversor sem transformador presentes na literatura. Após isso, obtém-se o modelo de modo comum de um conversor de três níveis e realiza-se a análise da resposta em frequência do sistema. Em seguida, são descritos os modos de operação do inversor proposto, incluindo os princípios de funcionamento do ramo de grampeamento. Simulações são realizadas para comparar o desempenho do conversor proposto com outras topologias a partir de vários parâmetros de desempenho, como nível da corrente de fuga, número de dispositivos, tensão sobre as chaves e perdas por condução e chaveamento. Por fim, o inversor sem transformador proposto é validado experimentalmente.

**Palavras-chave:** Inversor sem transformador, sistemas fotovoltaicos, corrente de fuga, alta eficiência.

# Abstract

This dissertation presents a new transformerless photovoltaic inverter topology for photovoltaic systems. The main challenge in transformerless systems is the leakage current that flows through the parasitic capacitances of the photovoltaic panels. To reduce this current, it is necessary to ensure that the common mode voltage does not exhibit high-frequency oscillations. Inverter topologies that mitigate leakage current can be divided into three main groups: common-ground inverters, zero-state decoupling inverters, and midpoint clamping inverters. In this work, a transformerless inverter with AC decoupling and DC bus midpoint clamping is proposed. In addition to reducing leakage current, it is expected that the inverter exhibits high efficiency compared to existing transformerless inverter topologies in the literature. Throughout the dissertation, an extensive review of transformerless inverter topologies in the literature is conducted. Subsequently, the common-mode model of a three-level converter is derived and the frequency response of the system is analyzed. The operation modes of the proposed inverter, including the principles of the clamping branch, are described. Simulations are performed to compare the performance of the proposed converter with other topologies based on various performance parameters, such as leakage current level, number of devices, voltage across the switches, and conduction and switching losses. Finally, the proposed transformerless inverter is experimentally validated.

**Keywords:** Transformerless inverter, photovoltaic systems, leakage current, high efficiency.

# Lista de ilustrações

|                                                                                                                                                              |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

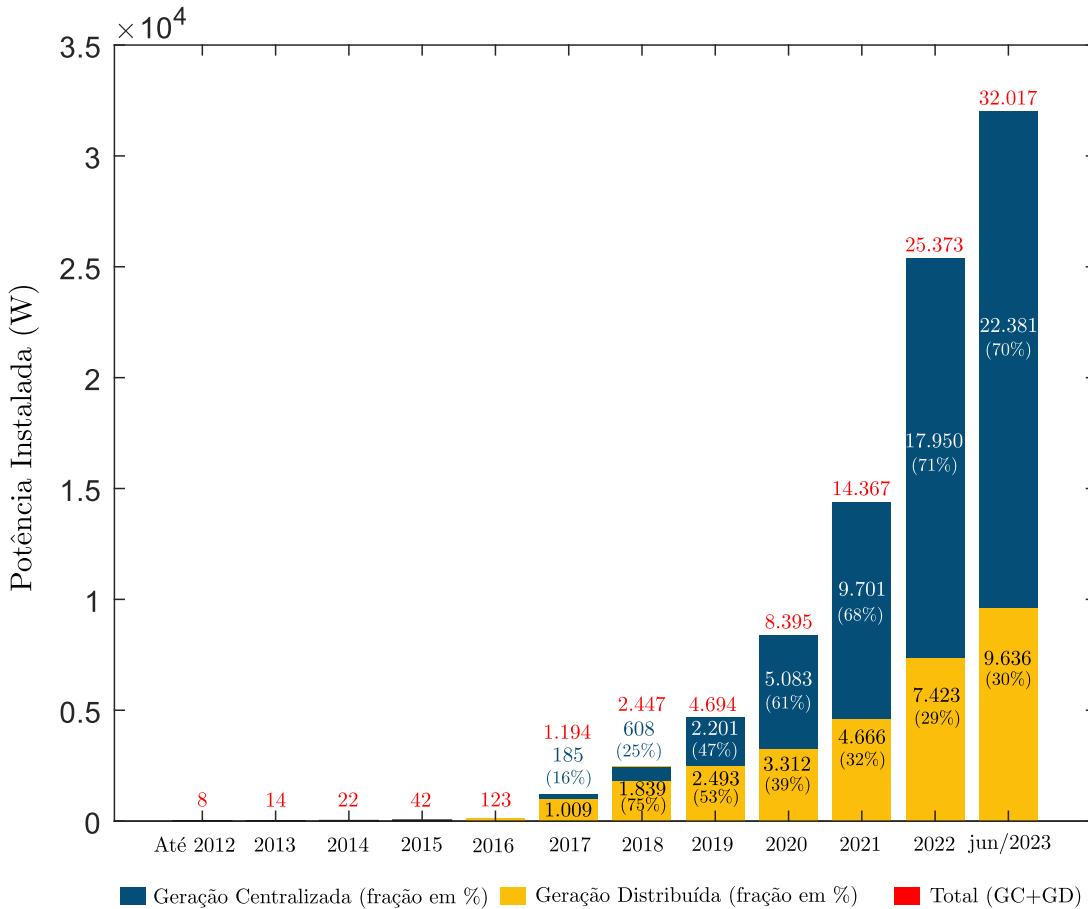

| Fig. 1 – Evolução da fonte solar fotovoltaica no Brasil . . . . .                                                                                            | 28 |

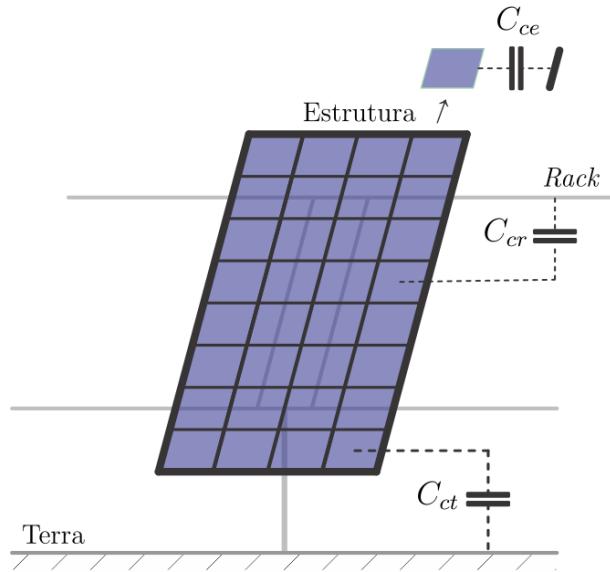

| Fig. 2 – Modelo concentrado das capacitâncias parasitas em um arranjo de módulos fotovoltaicos. . . . .                                                      | 34 |

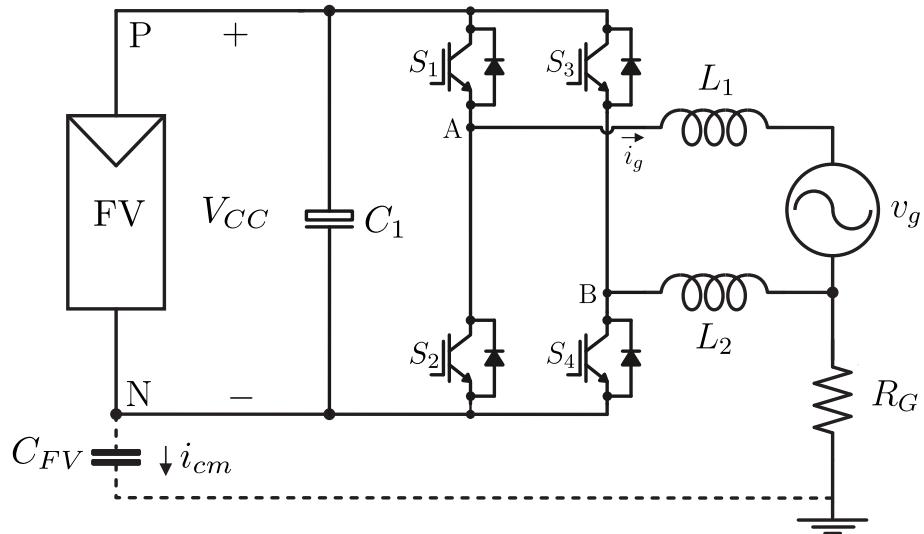

| Fig. 3 – Modelo geral de um inversor fotovoltaico sem transformador. . . . .                                                                                 | 35 |

| Fig. 4 – Modelo de modo comum de um inversor fotovoltaico sem transformador. .                                                                               | 36 |

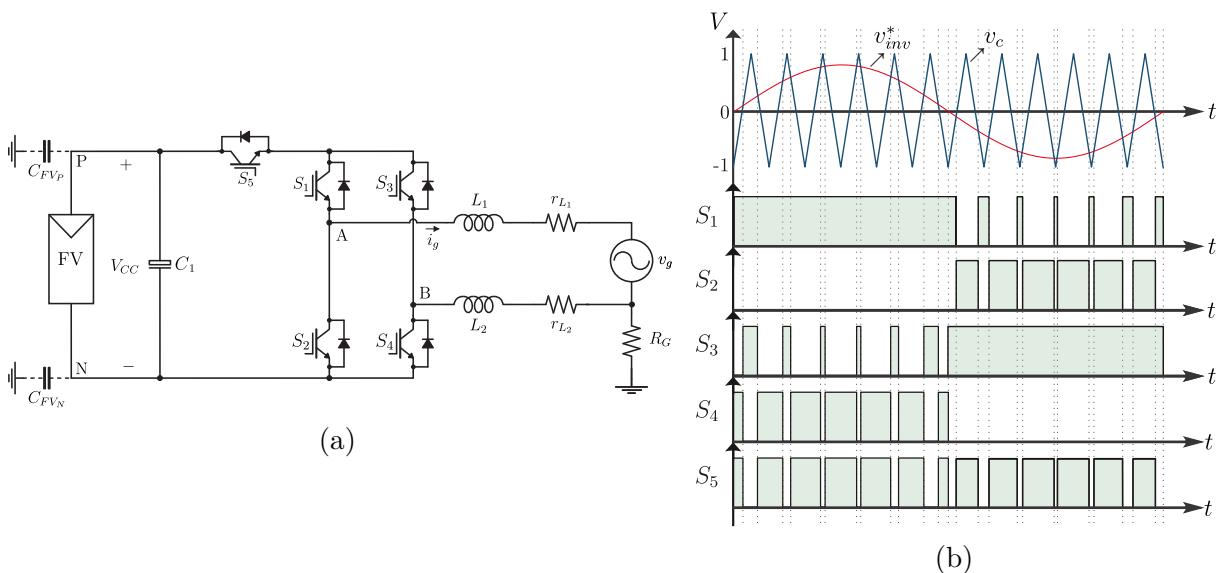

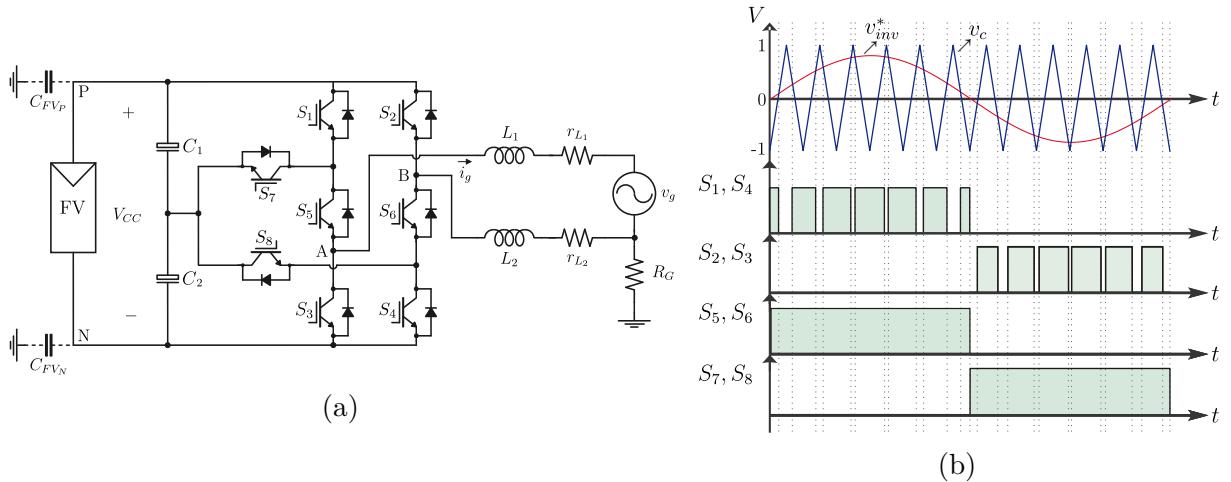

| Fig. 5 – Estrutura (a) e pulsos de chaveamento (b) do inversor NPC. . . . .                                                                                  | 39 |

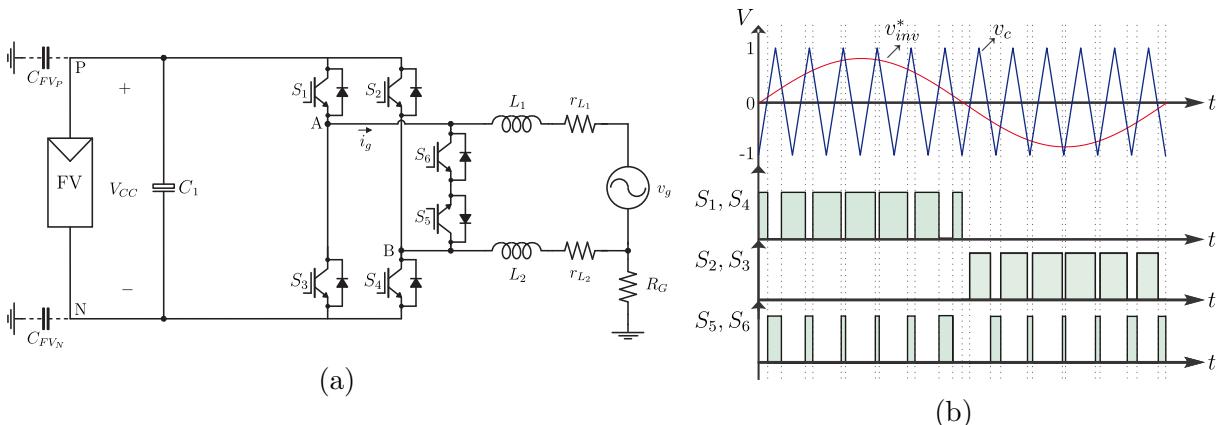

| Fig. 6 – Estrutura (a) e pulsos de chaveamento (b) do inversor ANPC. . . . .                                                                                 | 40 |

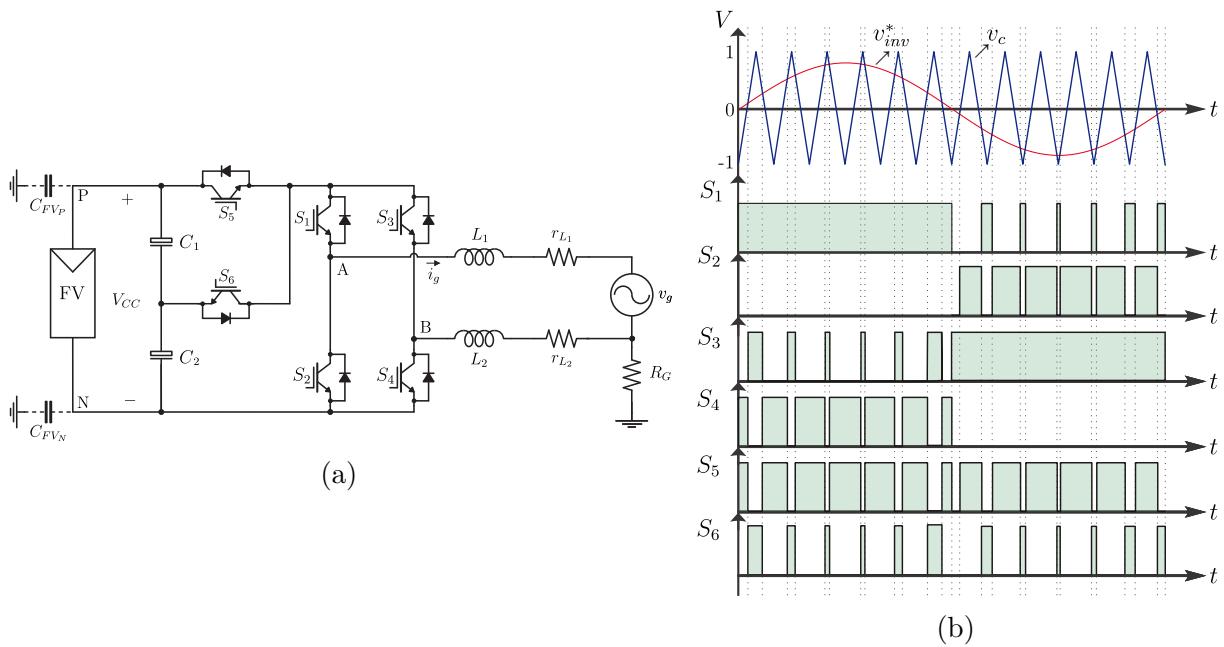

| Fig. 7 – Estrutura (a) e pulsos de chaveamento (b) do inversor Tipo T. . . . .                                                                               | 41 |

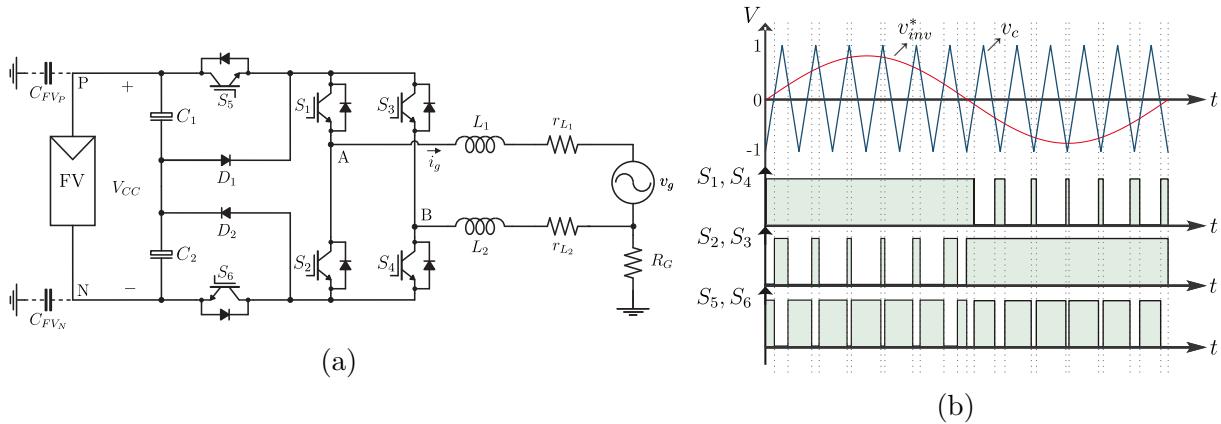

| Fig. 8 – Estrutura (a) e pulsos de chaveamento (b) do inversor H5. . . . .                                                                                   | 43 |

| Fig. 9 – Estrutura (a) e pulsos de chaveamento (b) do inversor HERIC. . . . .                                                                                | 44 |

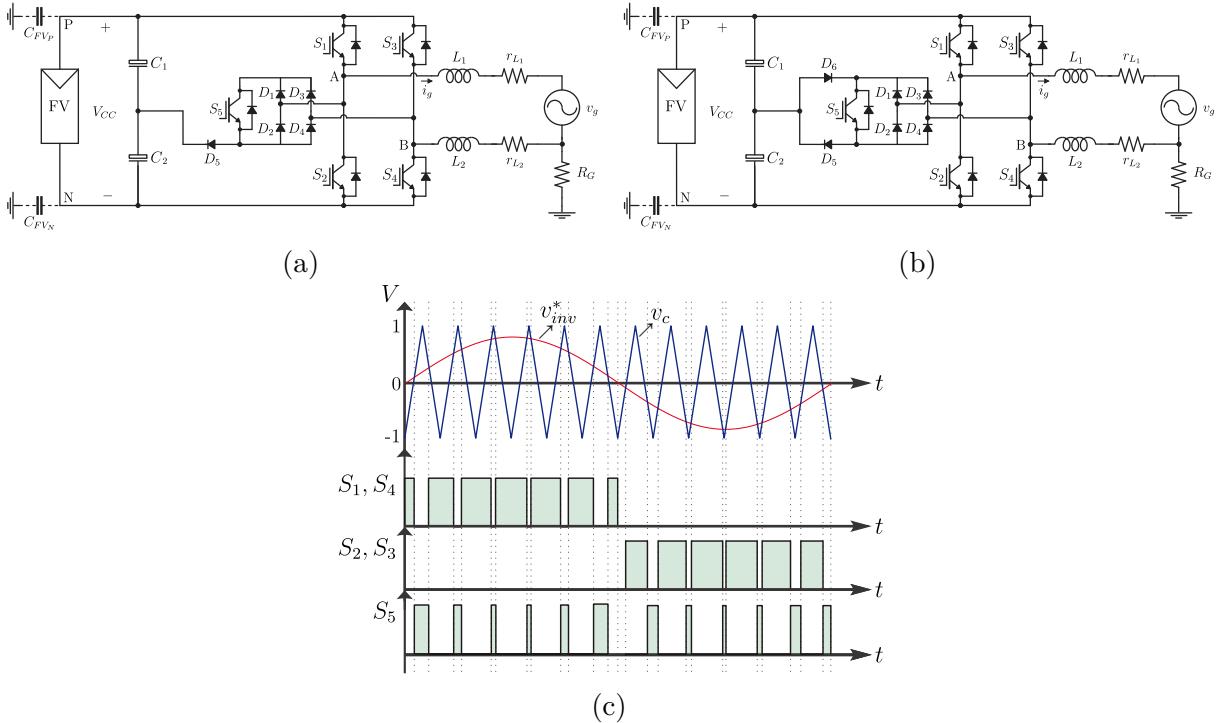

| Fig. 10 – Estrutura (a) e pulsos de chaveamento (b) do inversor H6 com diodos. .                                                                             | 45 |

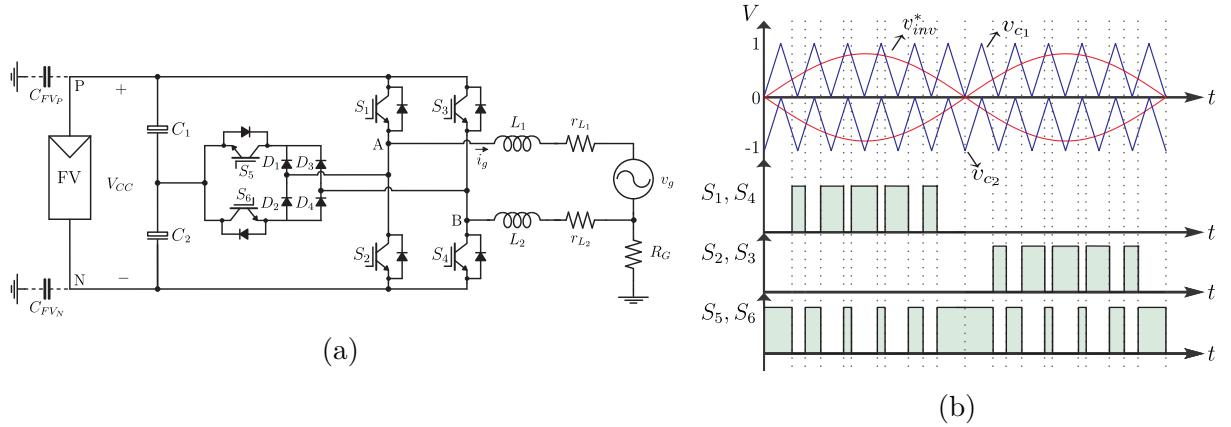

| Fig. 11 – Estrutura (a) e pulsos de chaveamento (b) do inversor oH5. . . . .                                                                                 | 46 |

| Fig. 12 – Estrutura (a) e pulsos de chaveamento (b) do inversor H6. . . . .                                                                                  | 48 |

| Fig. 13 – Estrutura (a) e pulsos de chaveamento (b) do inversor PN-NPC. . . . .                                                                              | 49 |

| Fig. 14 – Estrutura inversor HB-ZVR (a), HB-ZVR-D (b) e pulsos de chaveamento aplicados em ambas as topologias (c). . . . .                                  | 50 |

| Fig. 15 – Estrutura (a) e pulsos de chaveamento (b) do inversor HB-ZVSCR. . . .                                                                              | 51 |

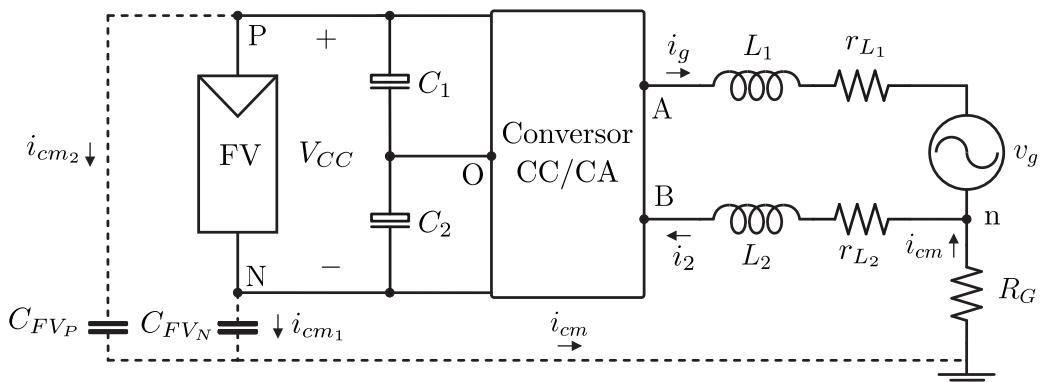

| Fig. 16 – Modelo geral de um inversor fotovoltaico sem transformador. . . . .                                                                                | 53 |

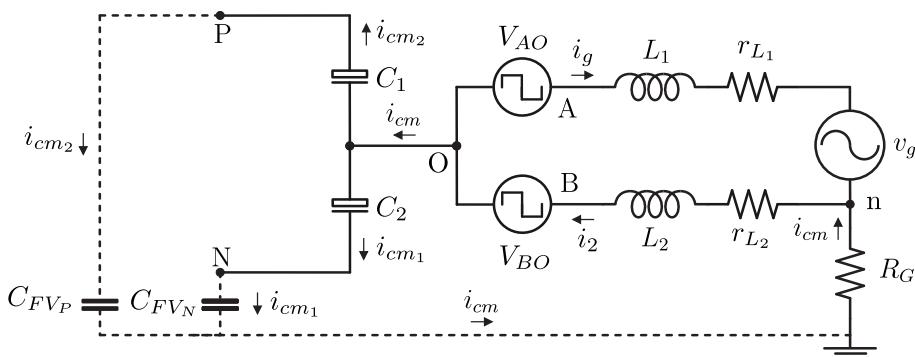

| Fig. 17 – Modelo de modo comum de um inversor fotovoltaico sem transformador com as tensões de polo $V_{AO}$ e $V_{BO}$ representando o conversor CC/CA. . . | 54 |

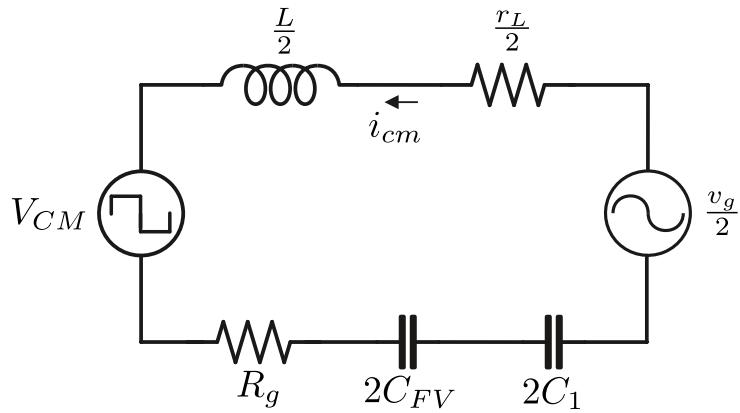

| Fig. 18 – Modelo de modo comum de um inversor monofásico sem transformador em um sistema fotovoltaico. . . . .                                               | 56 |

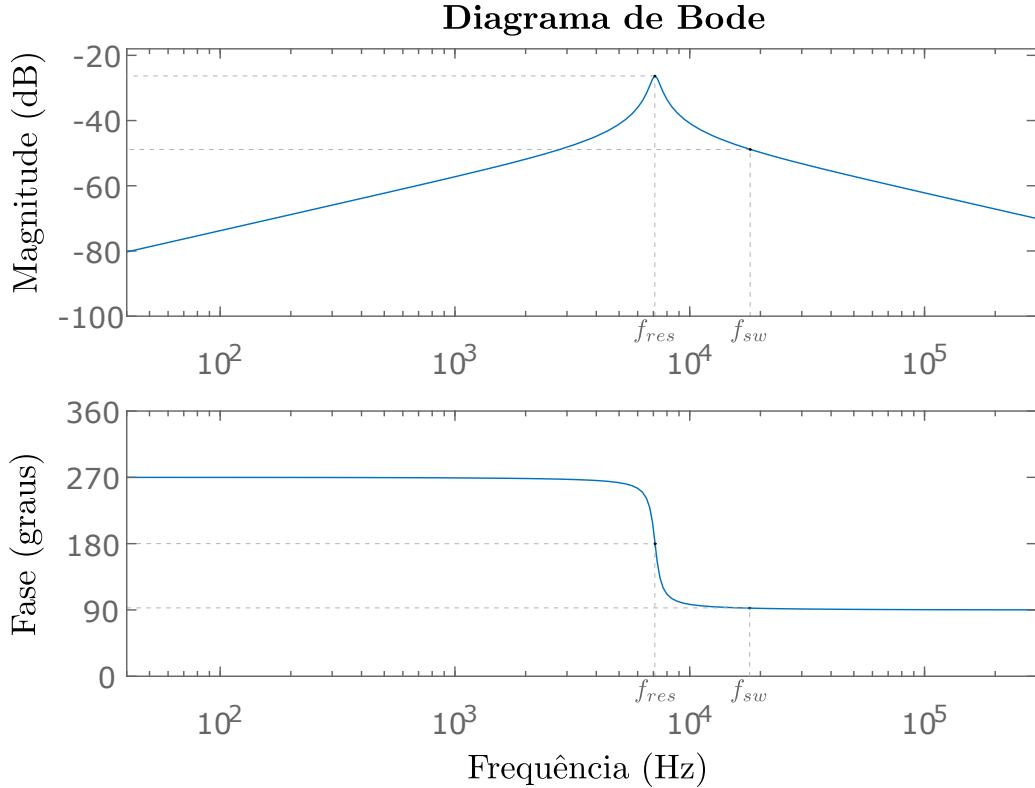

| Fig. 19 – Diagrama de Bode da corrente $i_{cm}$ em relação à tensão de modo comum $V_{CM}$ . . . . .                                                         | 57 |

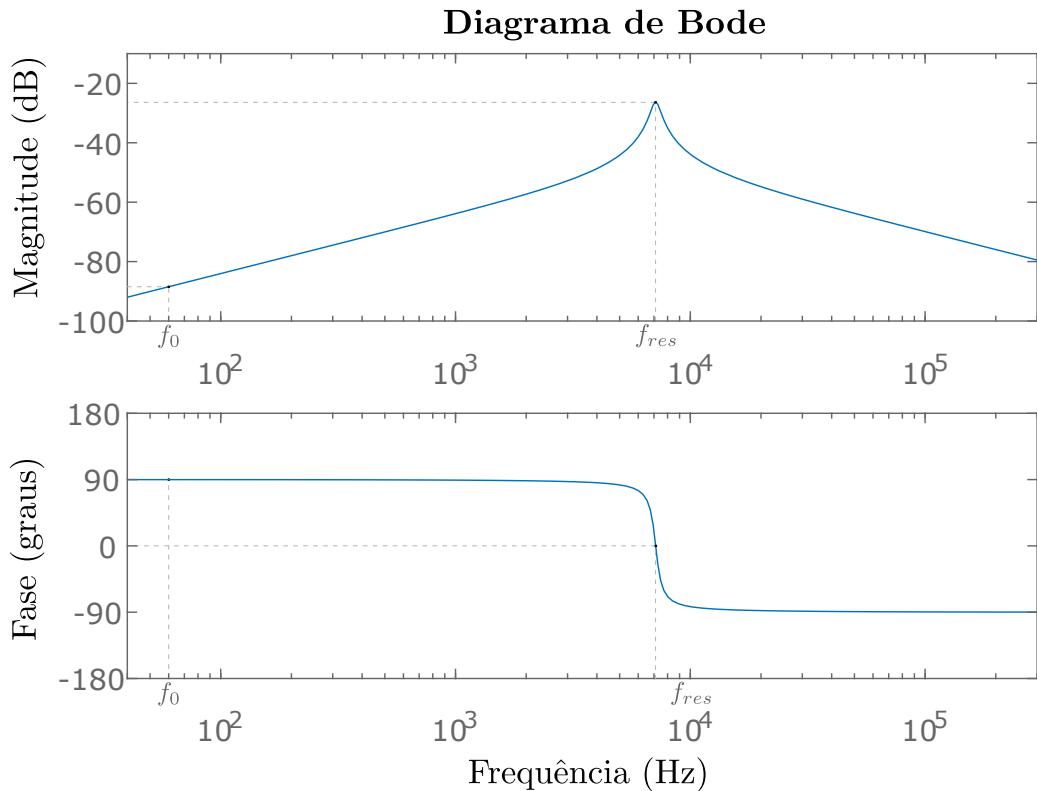

| Fig. 20 – Diagrama de Bode da corrente $i_{cm}$ em relação à tensão da rede elétrica $v_g$ . .                                                               | 58 |

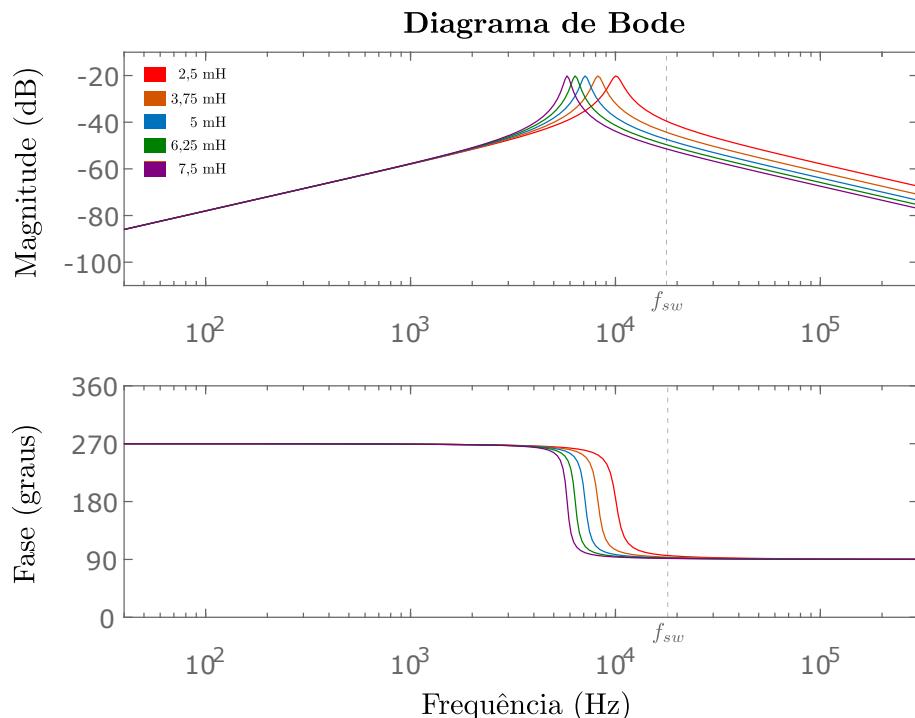

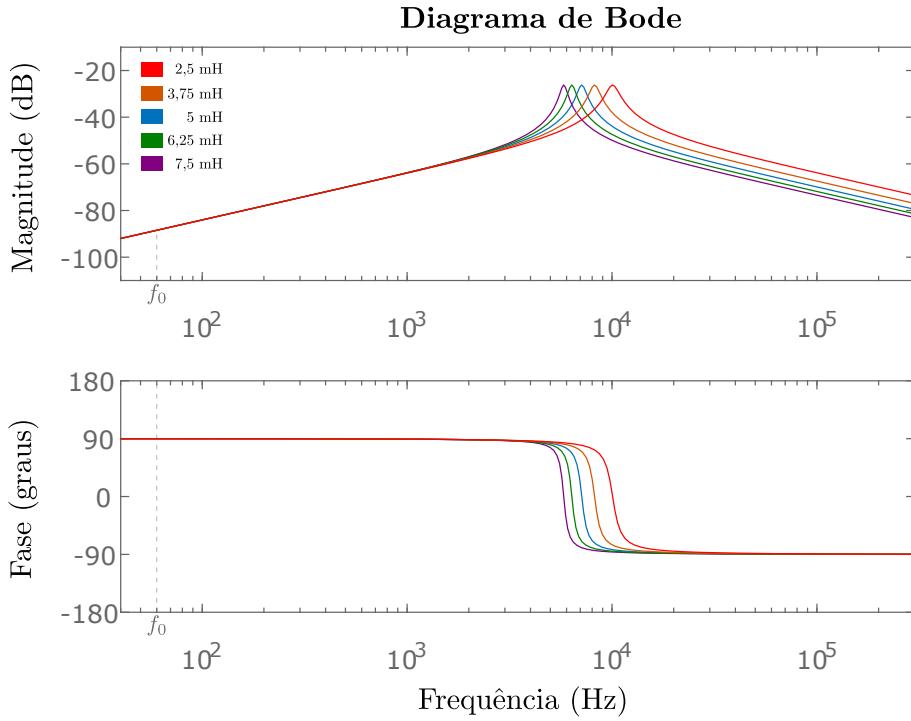

| Fig. 21 – Diagrama de Bode da corrente $i_{cm}$ em relação à tensão de modo comum $V_{CM}$ a partir da variação da indutância de filtro. . . . .             | 59 |

| Fig. 22 – Diagrama de Bode da corrente $i_{cm}$ em relação à tensão da rede elétrica $v_g$ a partir da variação da indutância de filtro. . . . .             | 60 |

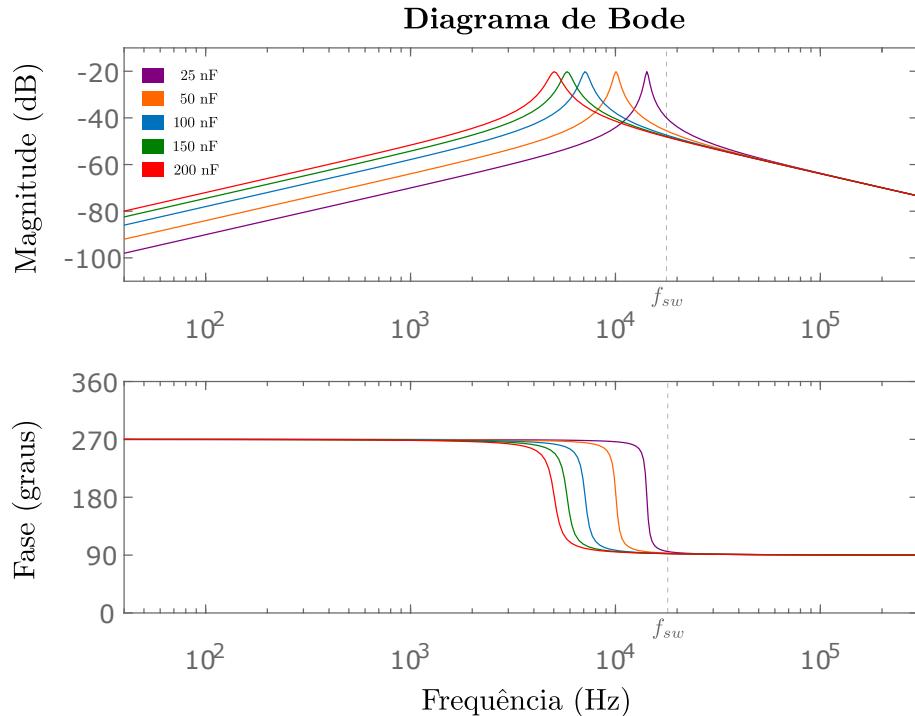

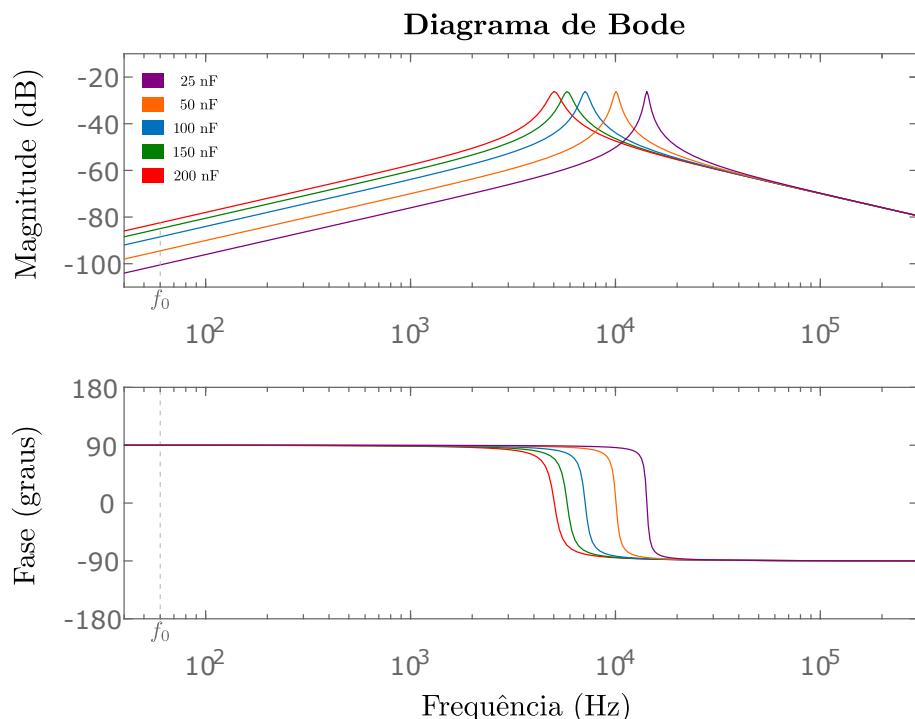

| Fig. 23 – Diagrama de Bode da corrente $i_{cm}$ em relação à tensão de modo comum $V_{CM}$ a partir da variação da capacitância parasita. . . . .            | 61 |

| Fig. 24 – Diagrama de Bode da corrente $i_{cm}$ em relação à tensão da rede elétrica $v_g$ a partir da variação da indutância de filtro. . . . .             | 61 |

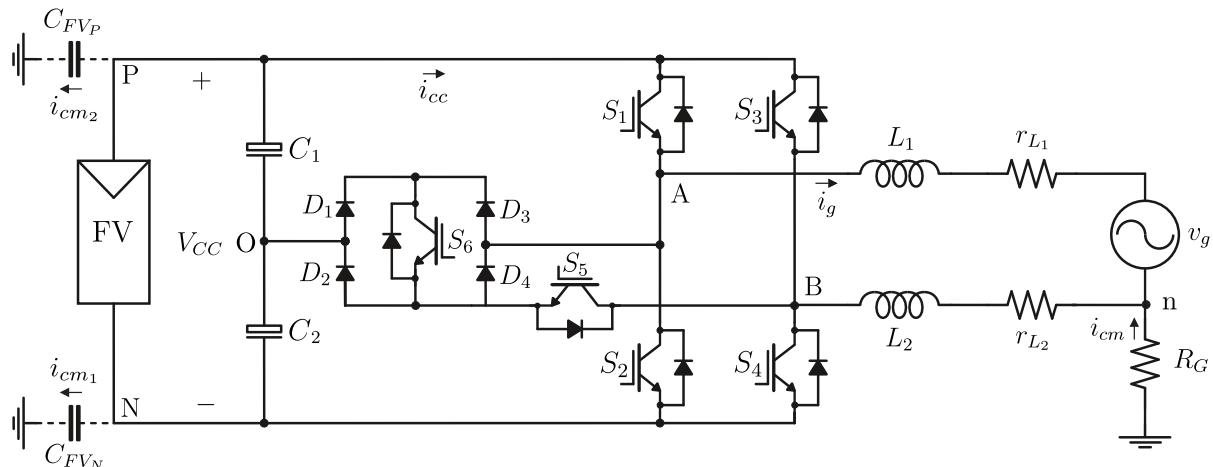

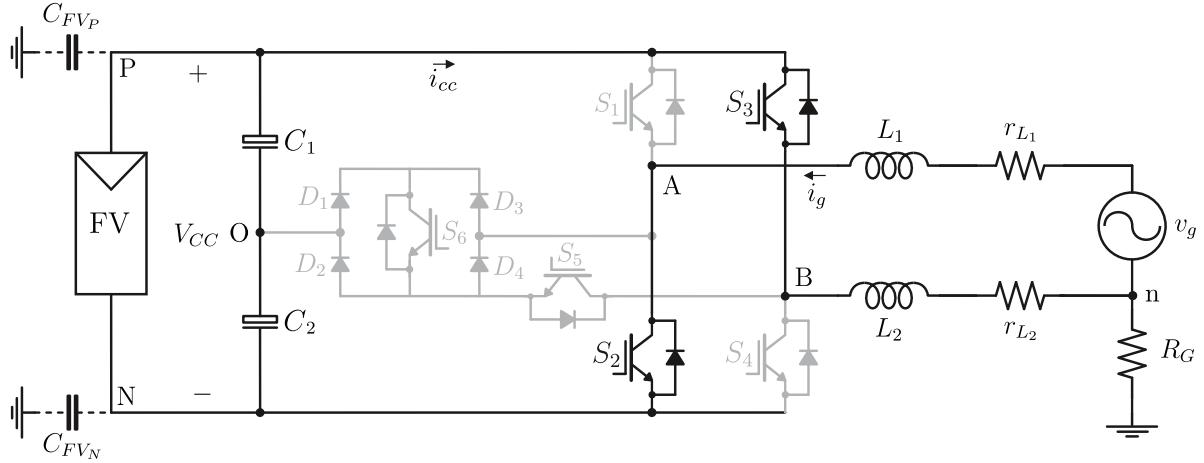

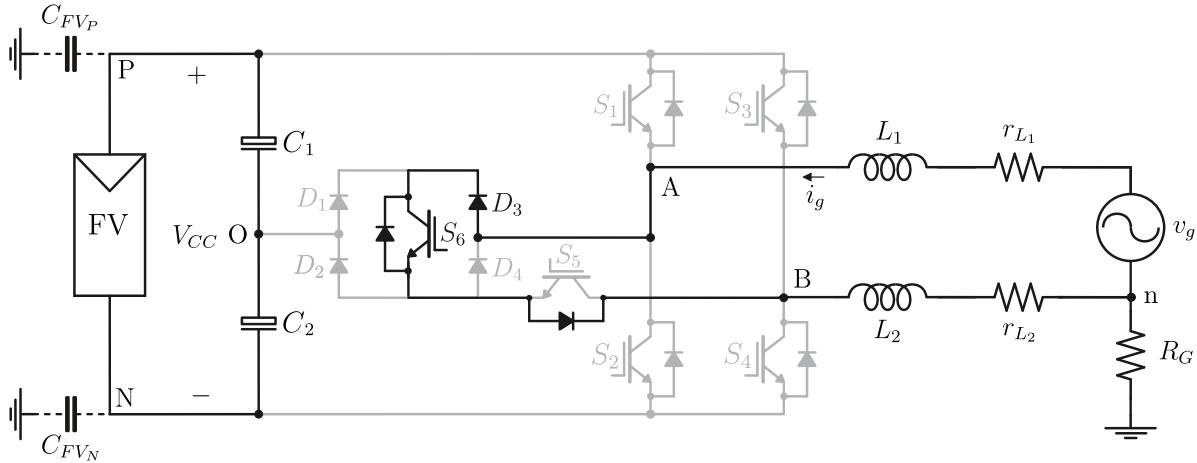

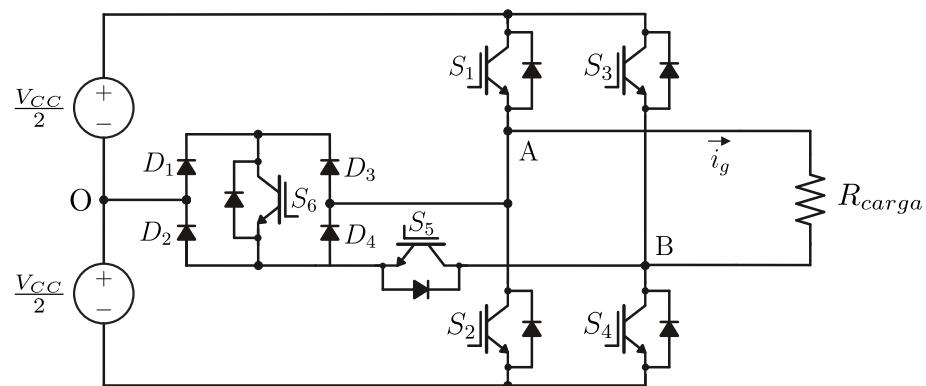

| Fig. 25 – Estrutura do inversor fotovoltaico monofásico sem transformador proposto. .                                                                        | 62 |

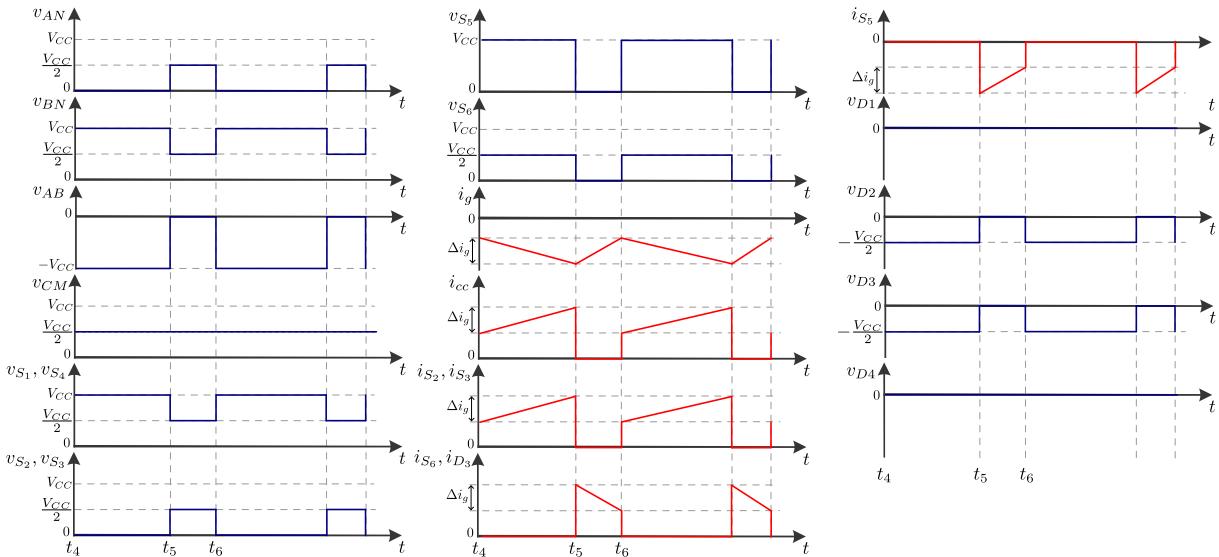

| Fig. 26 – Tensões e correntes do inversor proposto durante o semiciclo positivo da corrente injetada na rede. . . . .                                        | 64 |

|                                                                                                                                                                                                                                                     |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

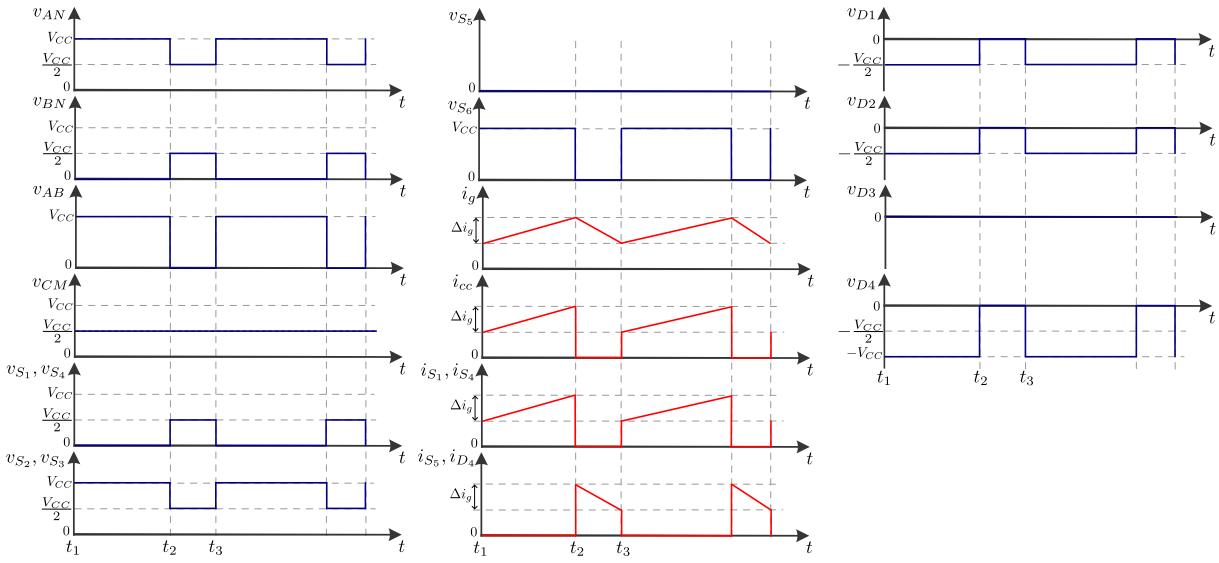

| Fig. 27 – Modo de condução - semiciclo positivo.                                                                                                                                                                                                    | 64 |

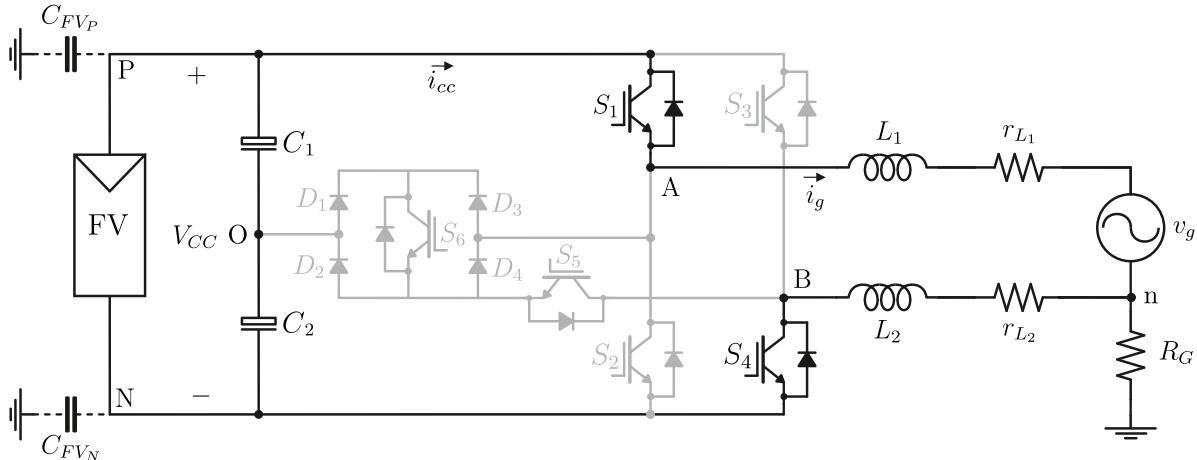

| Fig. 28 – Modo de roda-livre - semiciclo positivo.                                                                                                                                                                                                  | 65 |

| Fig. 29 – Tensões e correntes do inversor proposto durante o semiciclo negativo da corrente injetada na rede.                                                                                                                                       | 66 |

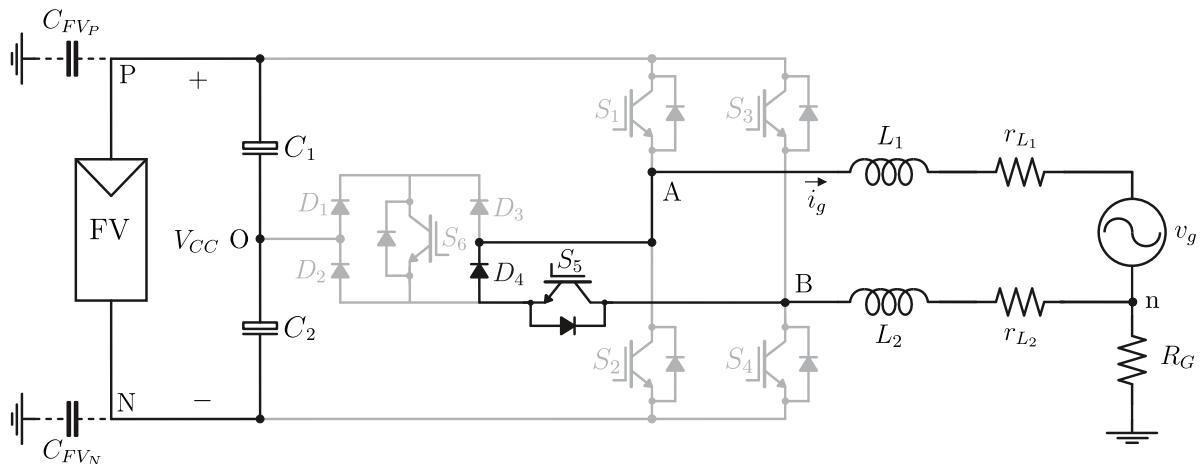

| Fig. 30 – Modo de condução - semiciclo negativo.                                                                                                                                                                                                    | 67 |

| Fig. 31 – Modo de roda-livre - semiciclo negativo.                                                                                                                                                                                                  | 68 |

| Fig. 32 – Modos de operação do ramo de grampeamento.                                                                                                                                                                                                | 70 |

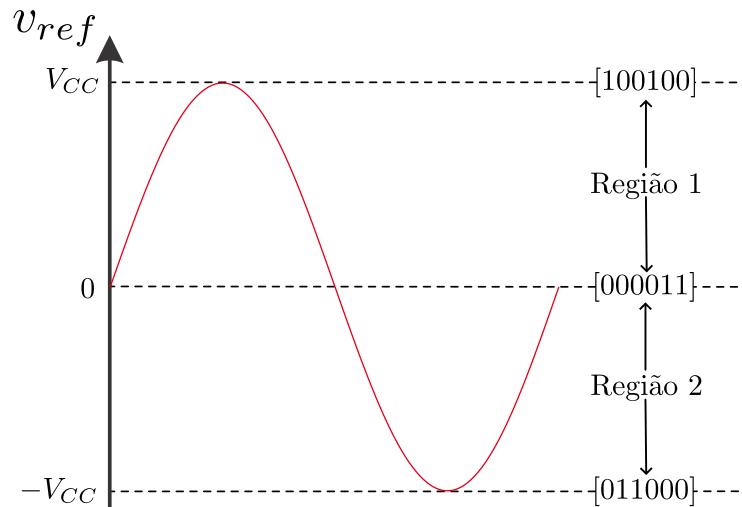

| Fig. 33 – Regiões da referência $v_{ref}$ e os estados das chaves em cada nível de tensão de saída.                                                                                                                                                 | 71 |

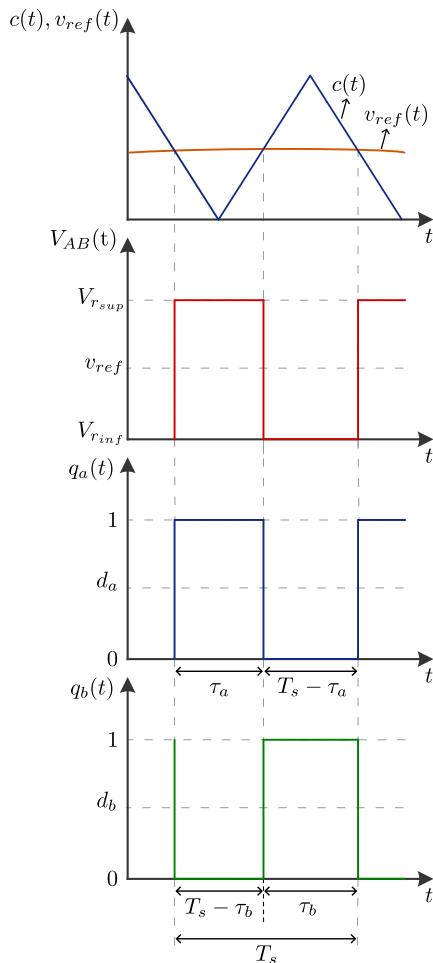

| Fig. 34 – Comparação entre sinal de referência $v_{ref}(t)$ e portadora triangular $c(t)$ , a fim de gerar sinais de chaveamento $q_a$ e $q_b$ e uma tensão de saída com valor médio $\overline{V_{AB}(t)} = v_{ref}$ .                             | 72 |

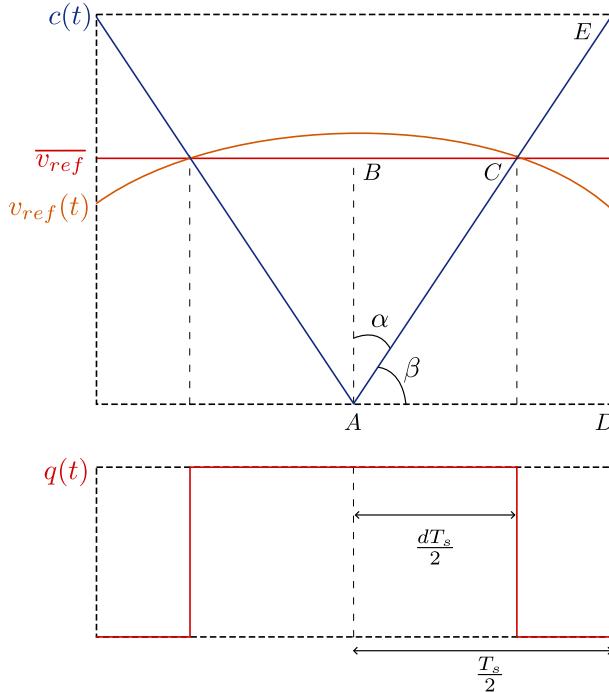

| Fig. 35 – Interpretação geométrica para o funcionamento da modulação PWM.                                                                                                                                                                           | 77 |

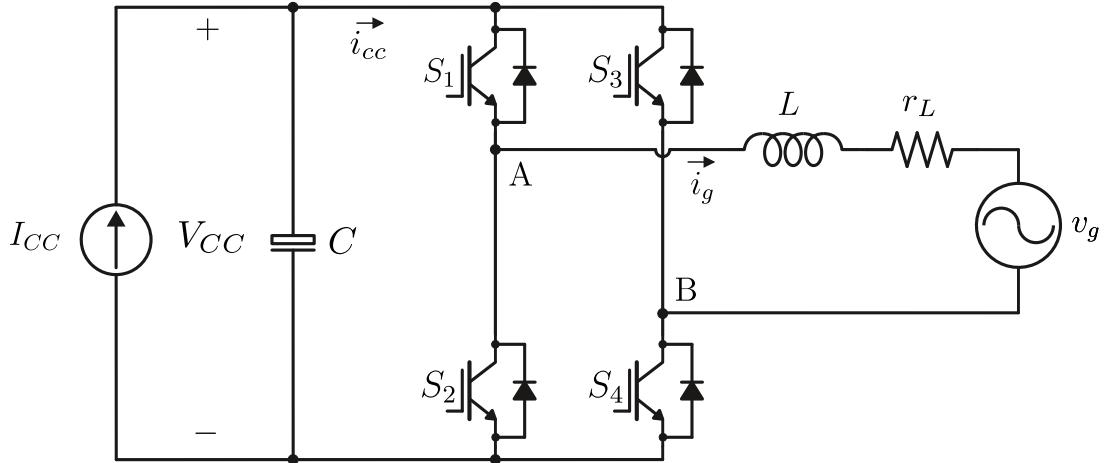

| Fig. 36 – Inversor monofásico conectado à rede.                                                                                                                                                                                                     | 79 |

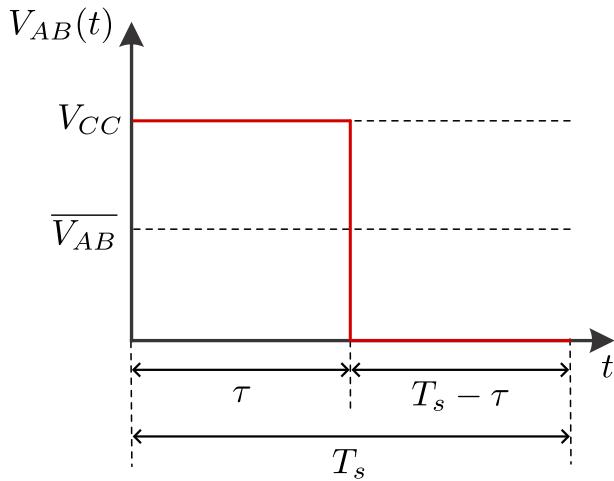

| Fig. 37 – Tensão $V_{AB}(t)$ na saída do inversor.                                                                                                                                                                                                  | 79 |

| Fig. 38 – Modelo equivalente do inversor monofásico conectado à rede.                                                                                                                                                                               | 81 |

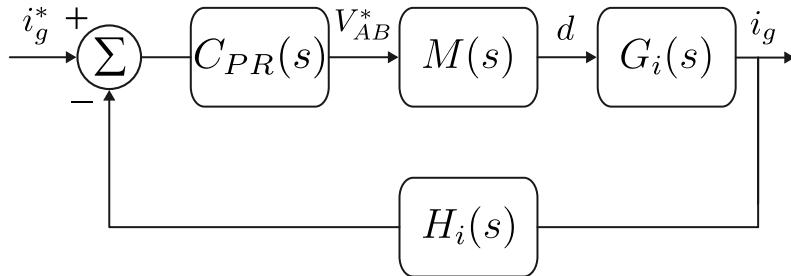

| Fig. 39 – Sistema de controle da corrente injetada na rede elétrica.                                                                                                                                                                                | 84 |

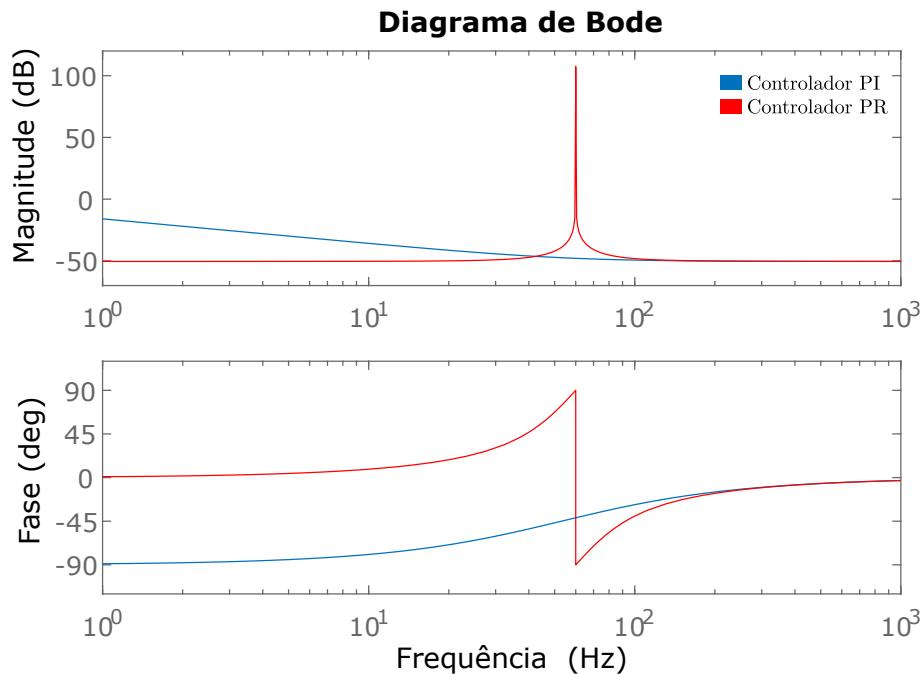

| Fig. 40 – Diagrama de Bode do controlador PR em comparação com o controlador PI convencional.                                                                                                                                                       | 85 |

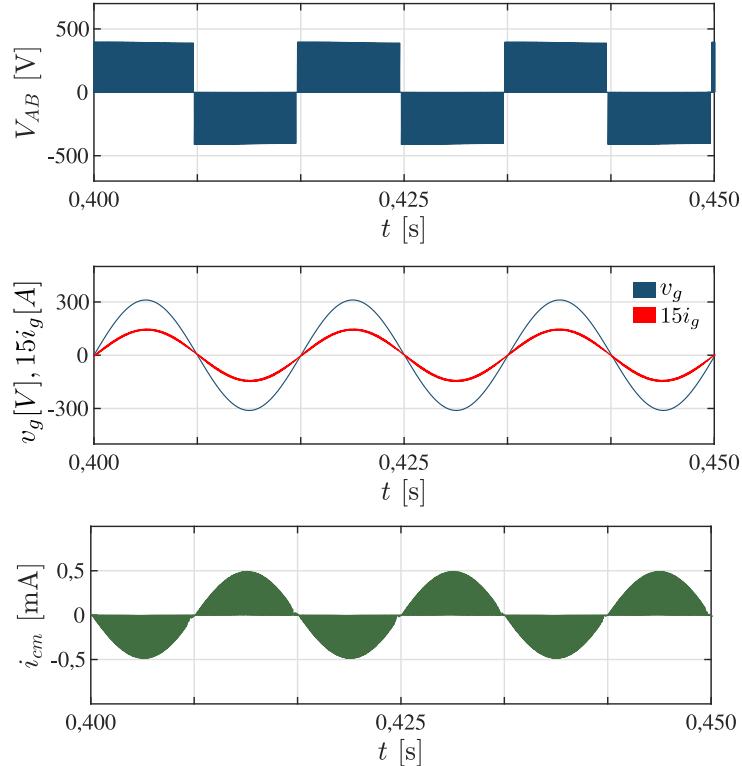

| Fig. 41 – Resultados de simulação para o inversor NPC meia-ponte: tensão diferencial de saída $V_{AB}$ , corrente injetada $i_g$ , tensão de rede $v_g$ e corrente de fuga $i_{cm}$ .                                                               | 93 |

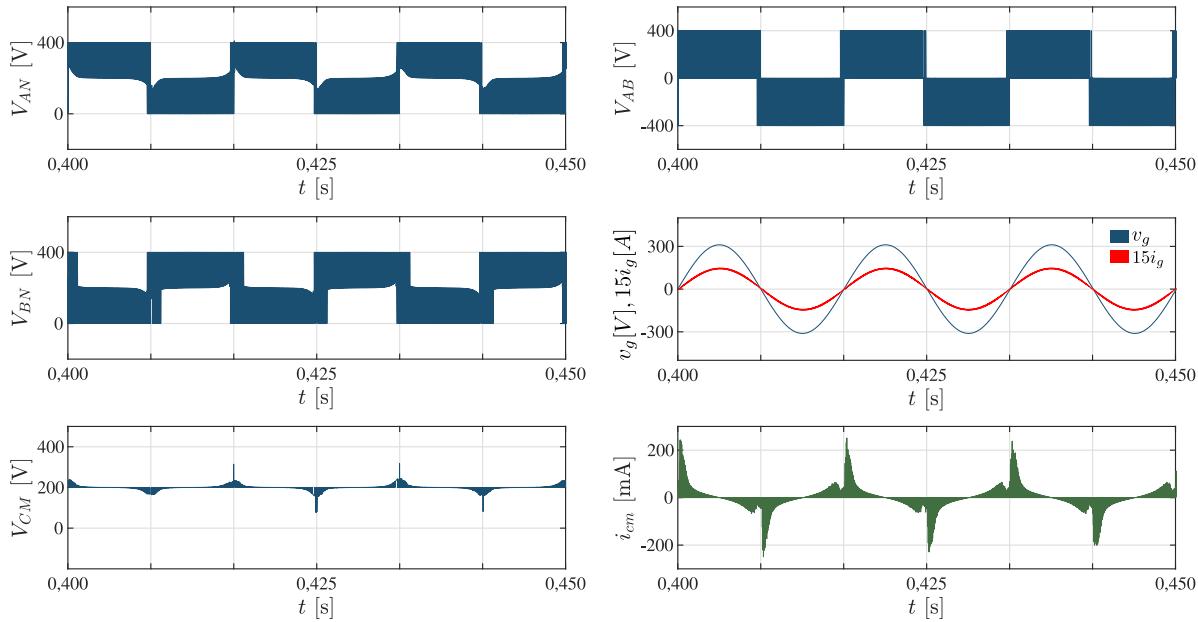

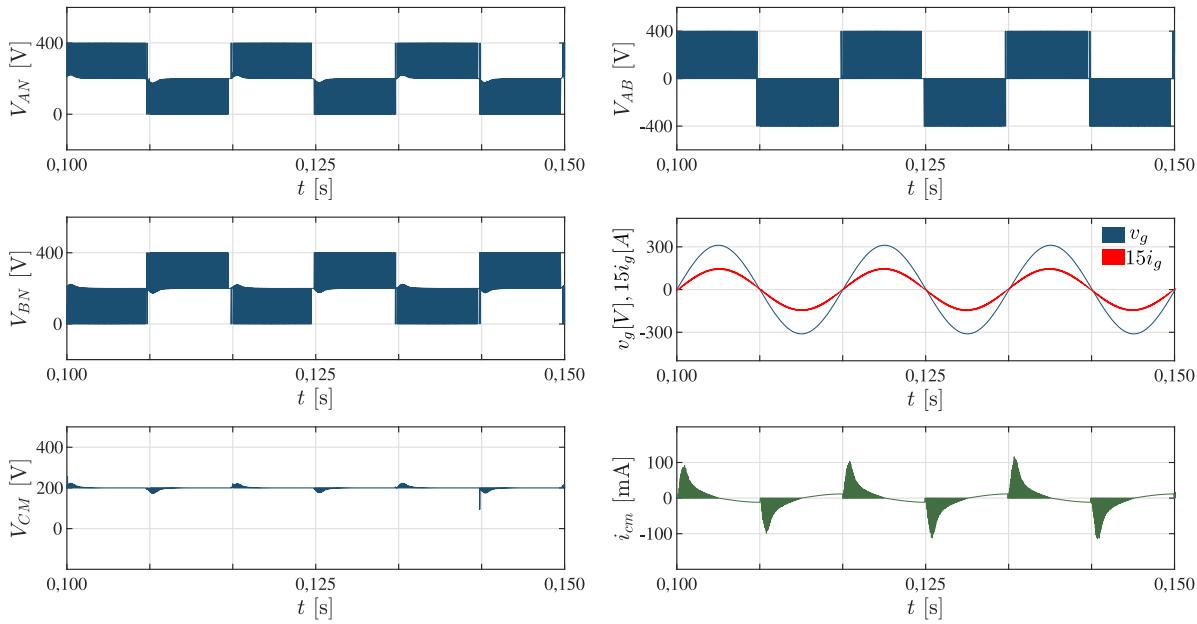

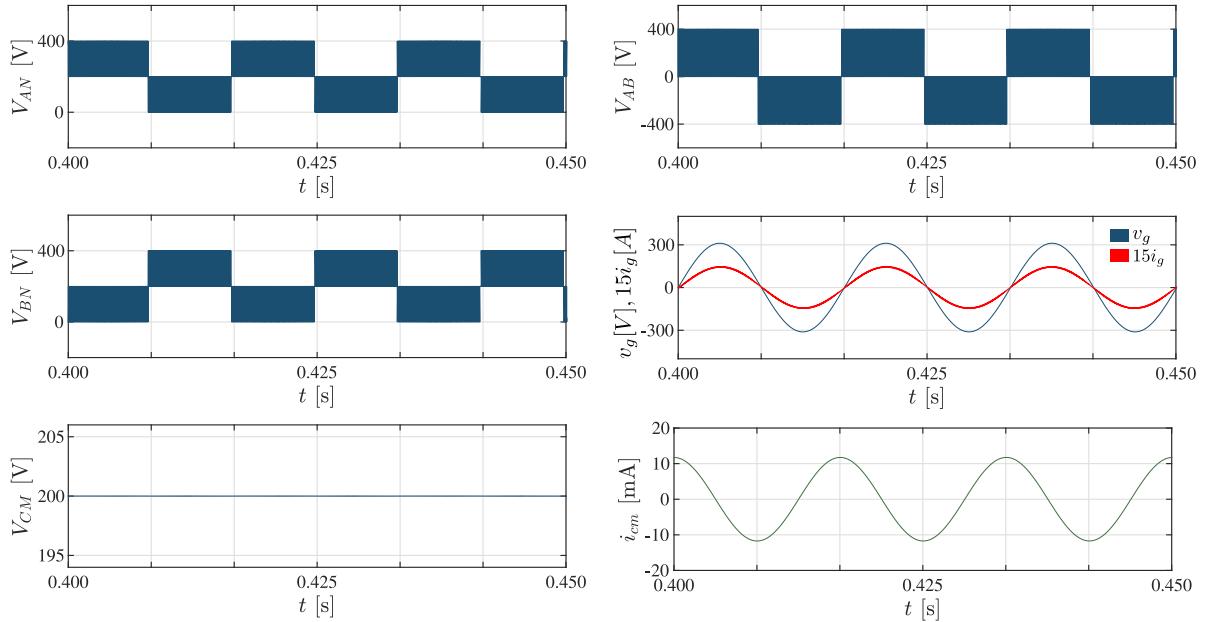

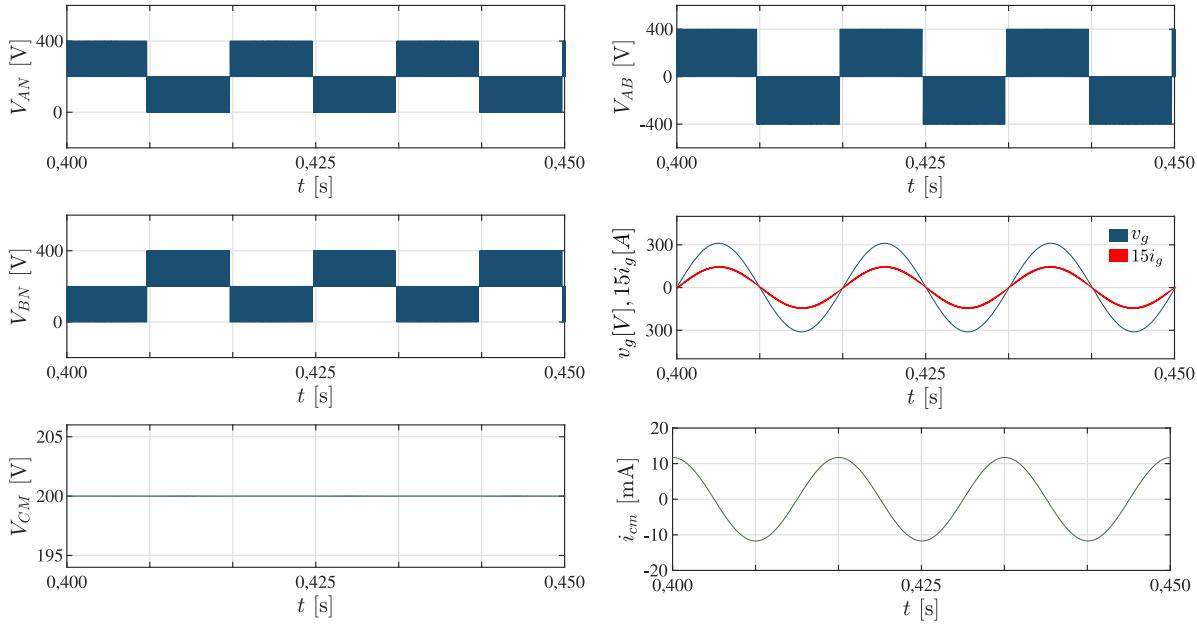

| Fig. 42 – Resultados de simulação para o inversor H5: tensões de polo $V_{AN}$ e $V_{BN}$ , tensão de modo comum $V_{CM}$ , tensão diferencial de saída $V_{AB}$ , corrente injetada $i_g$ , tensão de rede $v_g$ e corrente de fuga $i_{cm}$ .     | 94 |

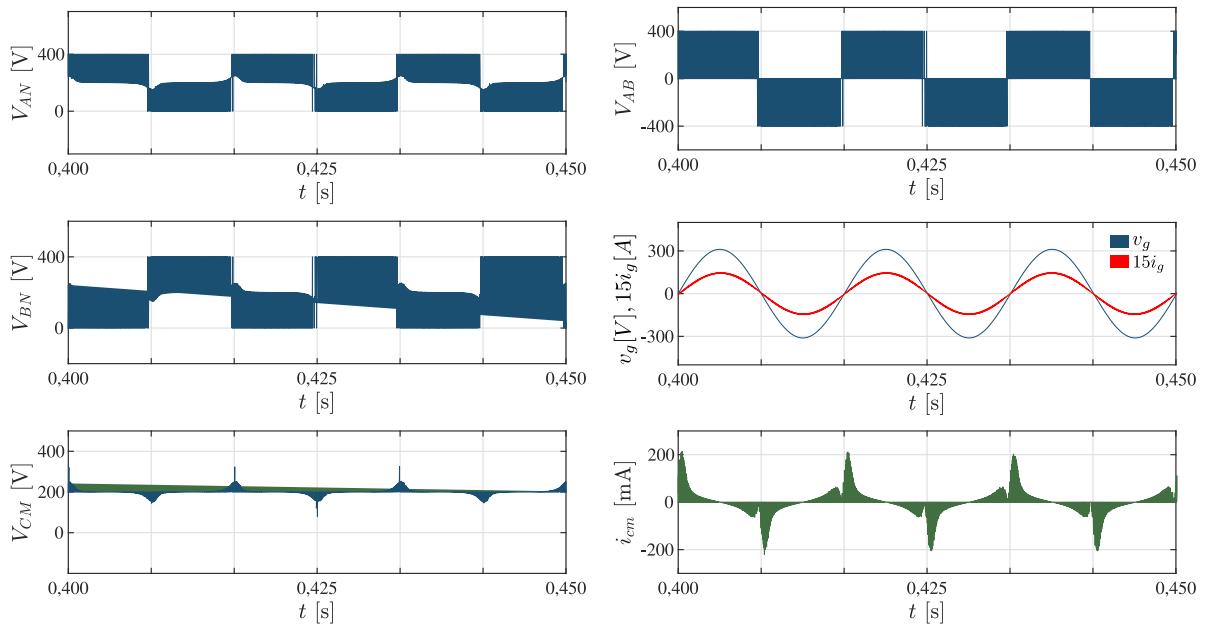

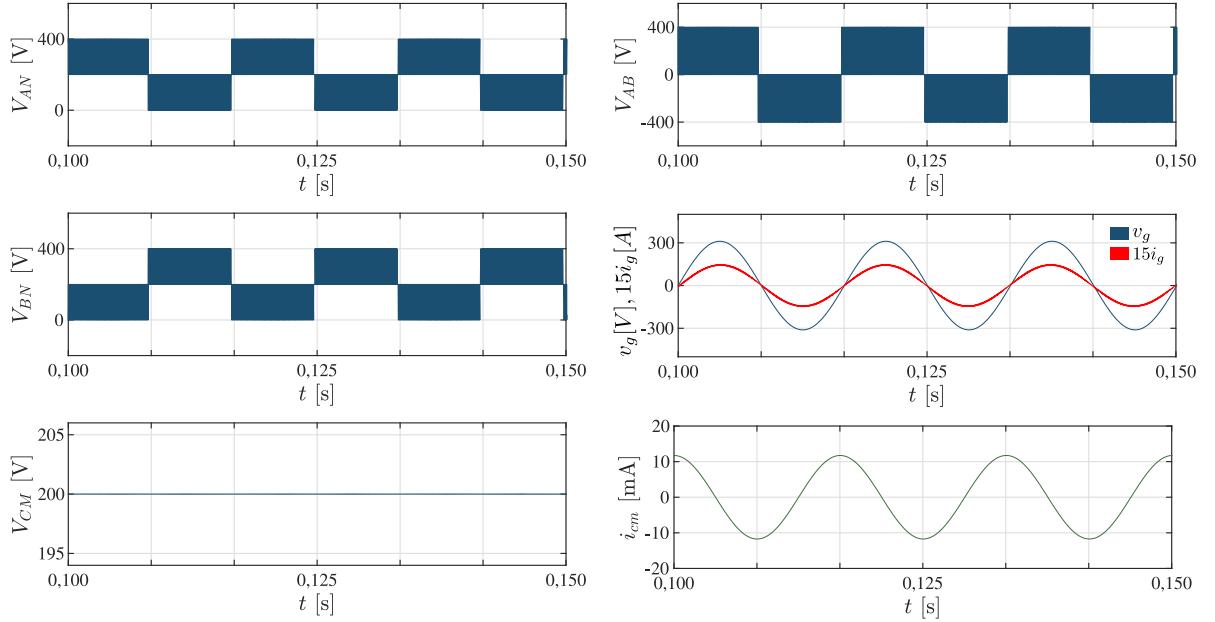

| Fig. 43 – Resultados de simulação para o inversor HERIC: tensões de polo $V_{AN}$ e $V_{BN}$ , tensão de modo comum $V_{CM}$ , tensão diferencial de saída $V_{AB}$ , corrente injetada $i_g$ , tensão de rede $v_g$ e corrente de fuga $i_{cm}$ .  | 95 |

| Fig. 44 – Resultados de simulação para o inversor OH5: tensões de polo $V_{AN}$ e $V_{BN}$ , tensão de modo comum $V_{CM}$ , tensão diferencial de saída $V_{AB}$ , corrente injetada $i_g$ , tensão de rede $v_g$ e corrente de fuga $i_{cm}$ .    | 97 |

| Fig. 45 – Resultados de simulação para o inversor H6: tensões de polo $V_{AN}$ e $V_{BN}$ , tensão de modo comum $V_{CM}$ , tensão diferencial de saída $V_{AB}$ , corrente injetada $i_g$ , tensão de rede $v_g$ e corrente de fuga $i_{cm}$ .     | 98 |

| Fig. 46 – Resultados de simulação para o inversor PN-NPC: tensões de polo $V_{AN}$ e $V_{BN}$ , tensão de modo comum $V_{CM}$ , tensão diferencial de saída $V_{AB}$ , corrente injetada $i_g$ , tensão de rede $v_g$ e corrente de fuga $i_{cm}$ . | 99 |

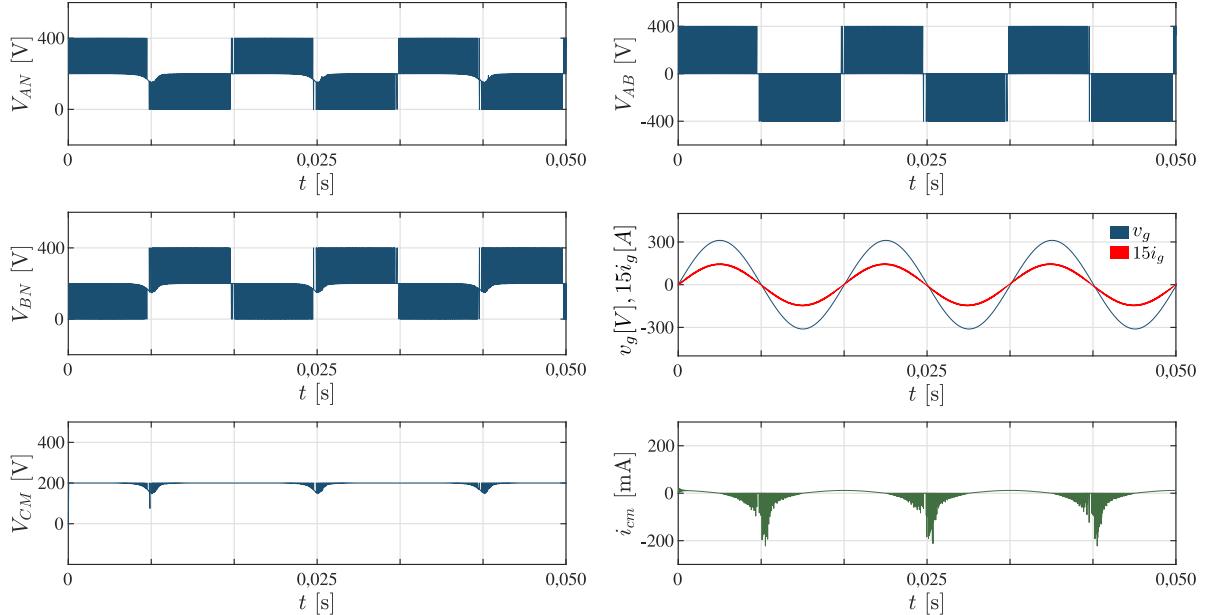

| Fig. 47 – Resultados de simulação para o inversor HB-ZVR: tensões de polo $V_{AN}$ e $V_{BN}$ , tensão de modo comum $V_{CM}$ , tensão diferencial de saída $V_{AB}$ , corrente injetada $i_g$ , tensão de rede $v_g$ e corrente de fuga $i_{cm}$ . | 99 |

|                                                                                                                                                                                                                                                               |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig. 48 – Resultados de simulação para o inversor HB-ZVR-D: tensões de polo $V_{AN}$ e $V_{BN}$ , tensão de modo comum $V_{CM}$ , tensão diferencial de saída $V_{AB}$ , corrente injetada $i_g$ , tensão de rede $v_g$ e corrente de fuga $i_{cm}$ . . . . . | 100 |

| Fig. 49 – Resultados de simulação para o inversor HB-ZVSCR: tensões de polo $V_{AN}$ e $V_{BN}$ , tensão de modo comum $V_{CM}$ , tensão diferencial de saída $V_{AB}$ , corrente injetada $i_g$ , tensão de rede $v_g$ e corrente de fuga $i_{cm}$ . . . . . | 101 |

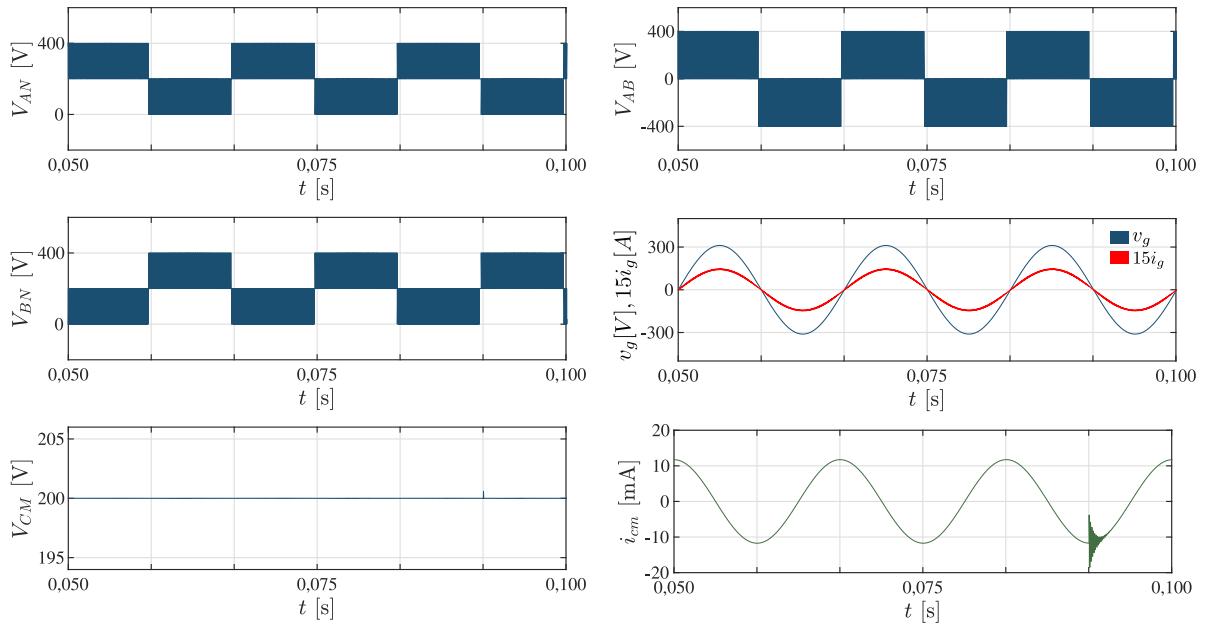

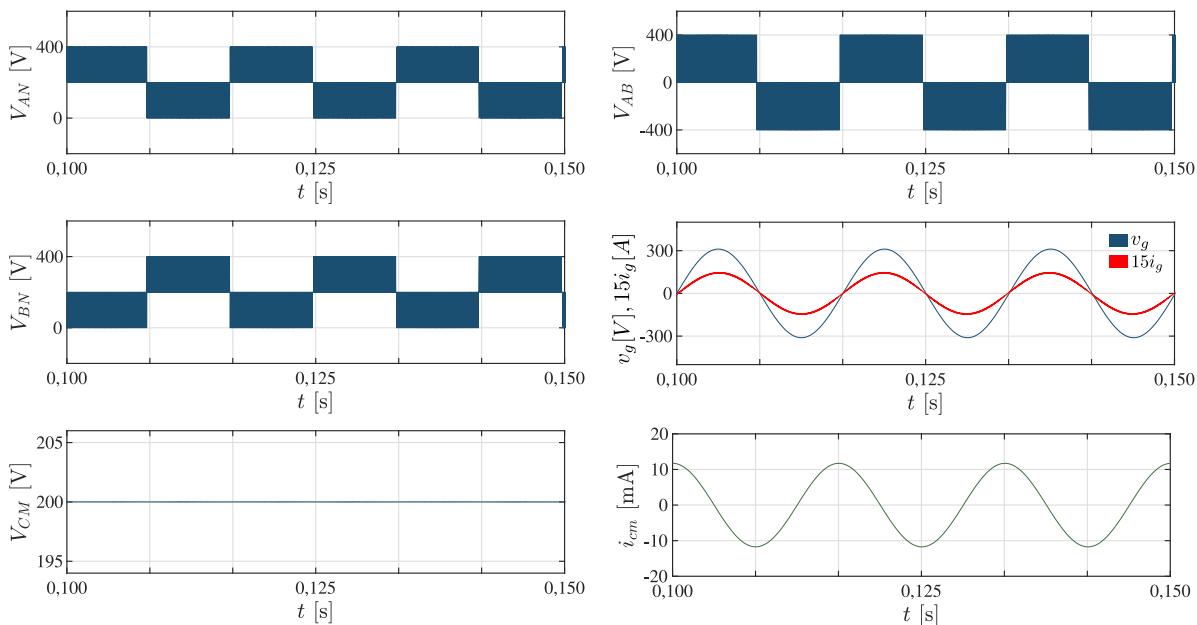

| Fig. 50 – Resultados de simulação para o inversor proposto: tensões de polo $V_{AN}$ e $V_{BN}$ , tensão de modo comum $V_{CM}$ , tensão diferencial de saída $V_{AB}$ , corrente injetada $i_g$ , tensão de rede $v_g$ e corrente de fuga $i_{cm}$ . . . . . | 102 |

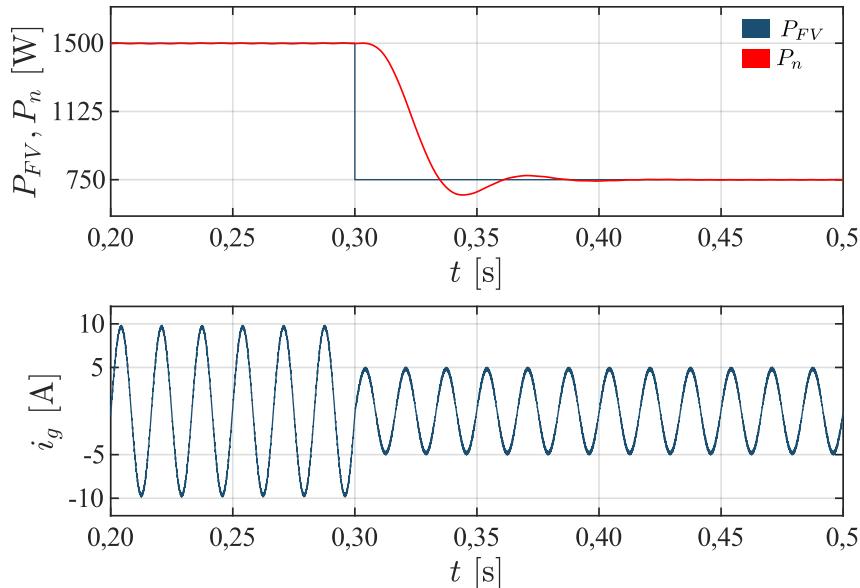

| Fig. 51 – Resposta do sistema a uma variação na potência gerada pelo painel fotovoltaico de 1500 W para 750 W. . . . .                                                                                                                                        | 103 |

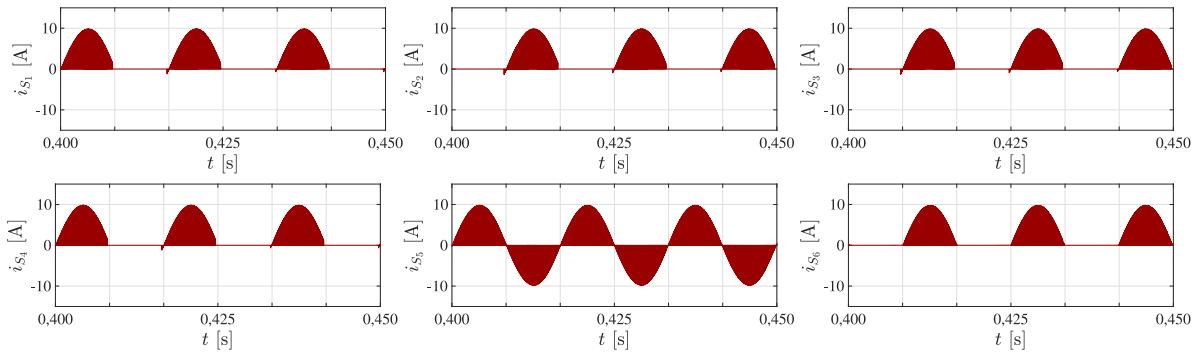

| Fig. 52 – Corrente das chaves do inversor fotovoltaico proposto. . . . .                                                                                                                                                                                      | 104 |

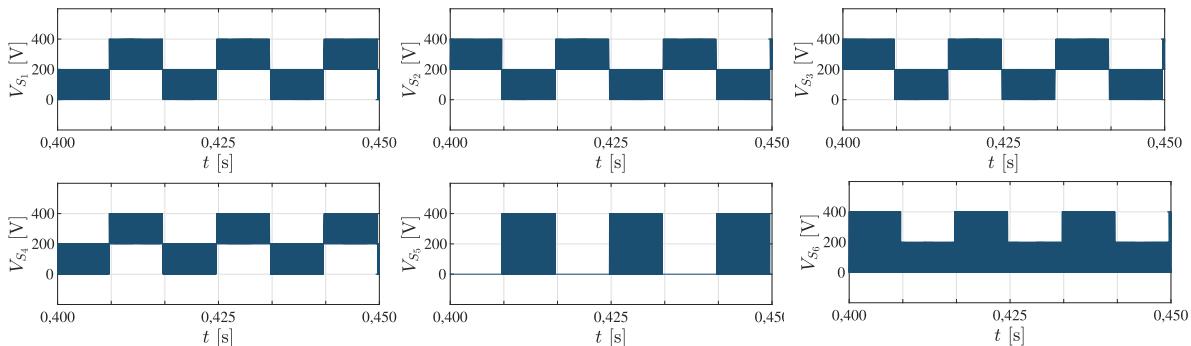

| Fig. 53 – Tensão sobre as chaves do inversor fotovoltaico proposto. . . . .                                                                                                                                                                                   | 104 |

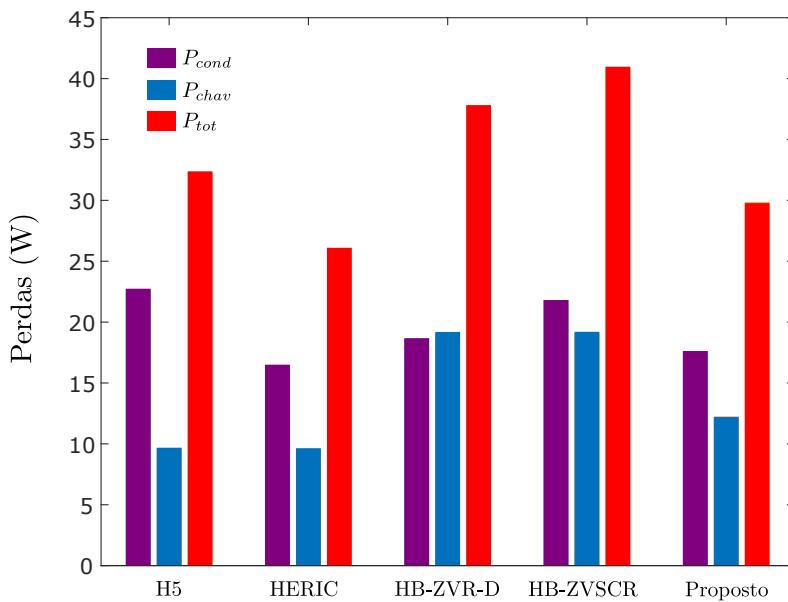

| Fig. 54 – Comparação das perdas do inversor proposto com topologias convencionais para uma potência nominal de 1,5 kW. . . . .                                                                                                                                | 110 |

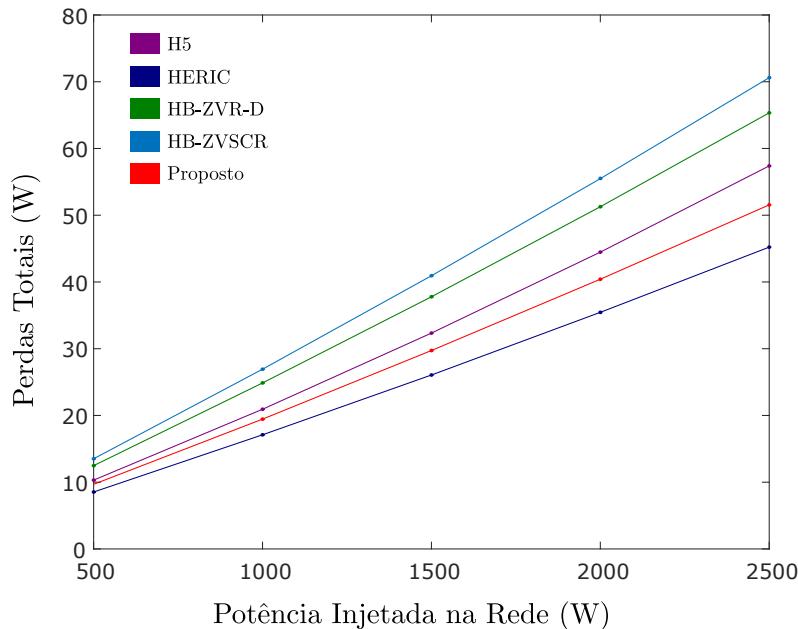

| Fig. 55 – Perdas totais para diferentes valores de potência injetada na rede: de 500 W a 2500 W. . . . .                                                                                                                                                      | 111 |

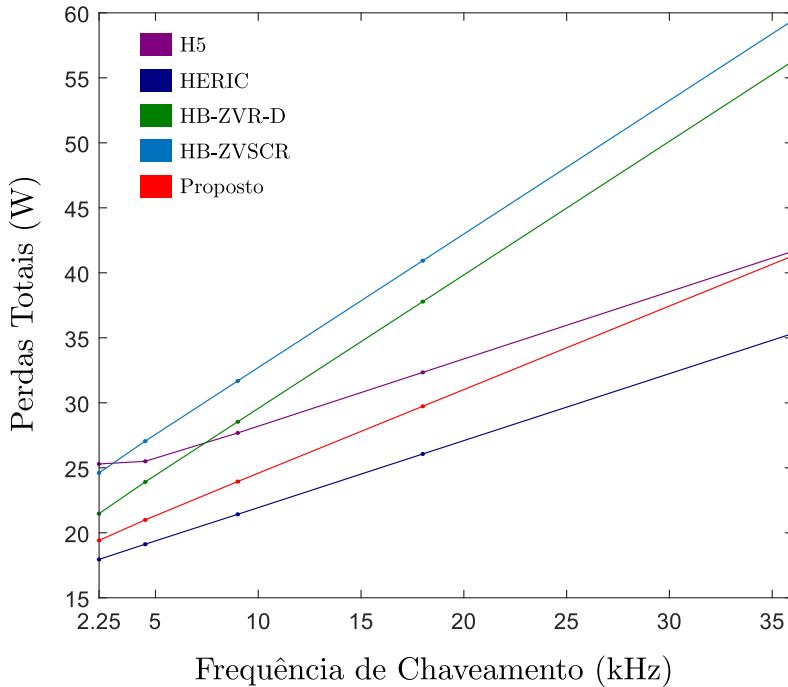

| Fig. 56 – Perdas totais para diferentes valores de frequência de chaveamento: de 2,25 kHz a 36 kHz. . . . .                                                                                                                                                   | 112 |

| Fig. 57 – Configuração do circuito para obtenção de resultados experimentais. . . .                                                                                                                                                                           | 113 |

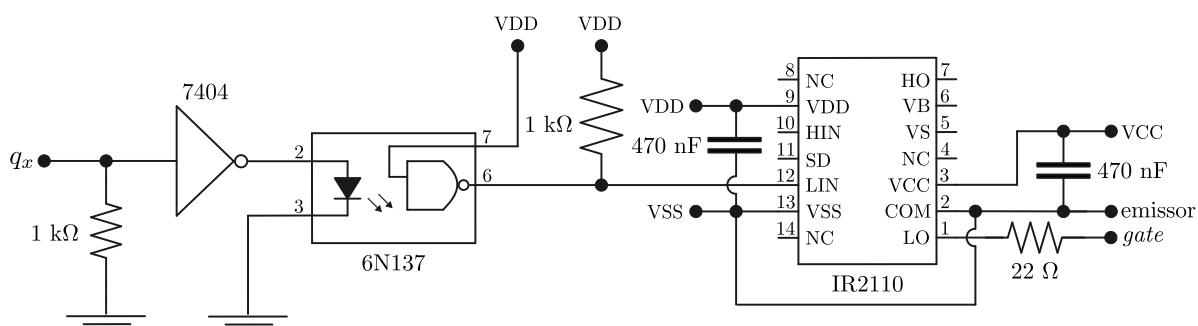

| Fig. 58 – Circuito para acionamento de um IGBT. . . . .                                                                                                                                                                                                       | 114 |

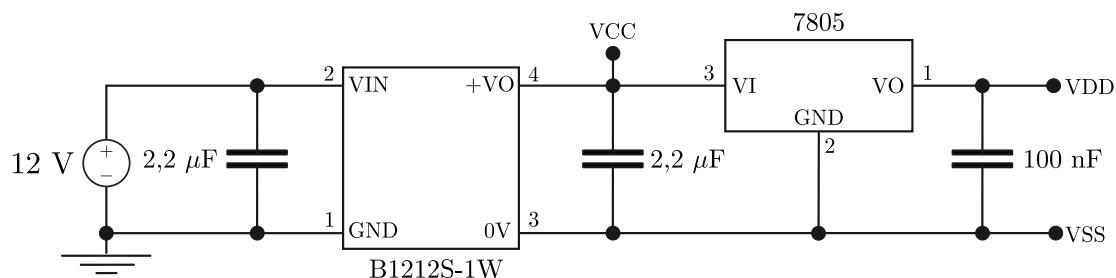

| Fig. 59 – Esquema de alimentação de um circuito de acionamento. . . . .                                                                                                                                                                                       | 115 |

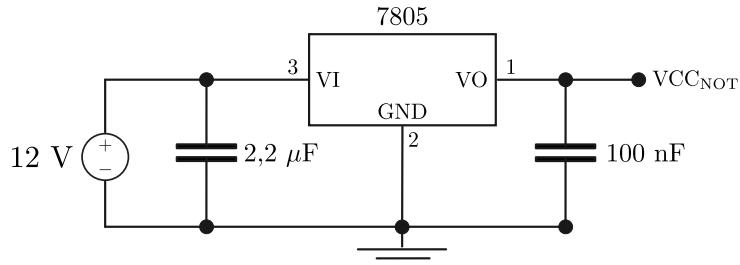

| Fig. 60 – Alimentação do CI 7404. . . . .                                                                                                                                                                                                                     | 116 |

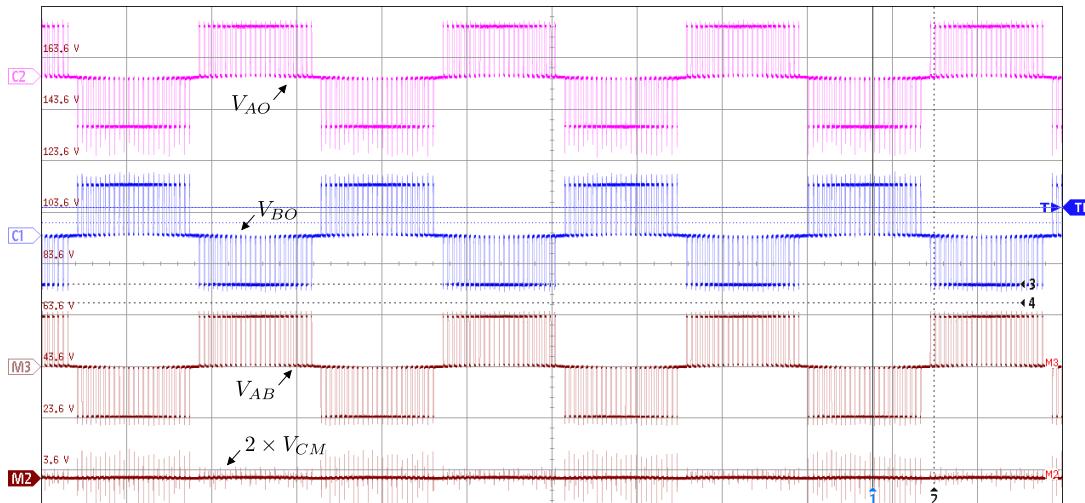

| Fig. 61 – Resultados experimentais para o inversor proposto: tensões de polo $V_{AO}$ e $V_{BO}$ , tensão diferencial de saída $V_{AB}$ e tensão de modo comum $V_{CM}$ . . . .                                                                               | 116 |

# Lista de tabelas

|                                                                                                                           |     |

|---------------------------------------------------------------------------------------------------------------------------|-----|

| Tab. 1 – Estados de chaveamento e tensões da topologia proposta.                                                          | 63  |

| Tab. 2 – Regiões do sinal modulante $v_{ref}$ , fórmulas dos ciclos de trabalho $d_x$ e fases das portadoras $\theta_x$ . | 76  |

| Tab. 3 – Estados da corrente $i_{cc}$ em um período de comutação.                                                         | 80  |

| Tab. 4 – Parâmetros de circuito utilizados nas simulações.                                                                | 91  |

| Tab. 5 – Valores de simulação para inversores meia-ponte com terra comum.                                                 | 92  |

| Tab. 6 – Valores de simulação para o inversor H5.                                                                         | 94  |

| Tab. 7 – Valores de simulação para os inversores com desacoplamento CA de estado-zero.                                    | 96  |

| Tab. 8 – Valores de simulação para os inversores oH5, H6 e PN-NPC.                                                        | 102 |

| Tab. 9 – Valores de simulação para os inversores HB-ZVR, HB-ZVR-D, HB-ZVSCR e o inversor proposto.                        | 103 |

| Tab. 10 – Resumo das topologias de inversor sem transformador estudadas.                                                  | 105 |

| Tab. 11 – Perdas de condução e chaveamento por dispositivo do inversor proposto para uma potência nominal de 1,5 kW.      | 109 |

| Tab. 12 – Perdas para uma variação de 500 a 2500 W na potência injetada na rede.                                          | 111 |

| Tab. 13 – Perdas para uma variação de 2,25 kHz a 36 kHz na frequência de chaveamento.                                     | 113 |

| Tab. 14 – Parâmetros de circuito utilizados no teste experimental.                                                        | 114 |

# Lista de abreviaturas e siglas

|                 |                                                          |

|-----------------|----------------------------------------------------------|

| <b>ANPC</b>     | <i>Active Neutral Point Clamped</i>                      |

| <b>CA</b>       | corrente alternada                                       |

| <b>CC</b>       | corrente contínua                                        |

| <b>FP</b>       | fator de potência                                        |

| <b>FV</b>       | Fotovoltaico                                             |

| <b>HERIC</b>    | <i>Highly Efficient and Reliable Inverter Concept</i>    |

| <b>HB-ZVR</b>   | <i>H-Bridge Zero Voltage Rectifier</i>                   |

| <b>HB-ZVSCR</b> | <i>H-Bridge Zero Voltage Switch-Controlled Rectifier</i> |

| <b>NPC</b>      | <i>Neutral Point Clamped</i>                             |

| <b>N-NPCC</b>   | <i>Negative Neutral Point Clamped Cell</i>               |

| <b>oH5</b>      | <i>Optimized H5</i>                                      |

| <b>PWM</b>      | <i>Pulse Width Modulation</i>                            |

| <b>P-NPCC</b>   | <i>Positive Neutral Point Clamped Cell</i>               |

| <b>PN-NPC</b>   | <i>Positive Negative Neutral Point Clamped</i>           |

| <b>PR</b>       | Proporcional-ressonante                                  |

| <b>PI</b>       | Proporcional-integral                                    |

| <b>SPWM</b>     | <i>Senooidal Pulse Width Modulation</i>                  |

| <b>THD</b>      | <i>total harmonic distortion</i>                         |

| $V_{CM}$        | tensão de modo comum                                     |

| <b>UCP</b>      | Unidade de Condicionamento de Potência                   |

| $V_{FP}$        | <i>freewheeling path voltage</i>                         |

# Listas de símbolos

|            |                                                                                              |

|------------|----------------------------------------------------------------------------------------------|

| $C_1$      | Capacitor do barramento CC.                                                                  |

| $C_2$      | Capacitor do barramento CC.                                                                  |

| $C_{ce}$   | Capacitância entre as células de silício do painel fotovoltaico e sua estrutura de alumínio. |

| $C_{cr}$   | Capacitância entre as células de silício do painel fotovoltaico e o <i>rack</i> de montagem. |

| $C_{ct}$   | Capacitância entre as células dos módulos fotovoltaicos e o solo.                            |

| $C_{FV}$   | Capacitância parasita equivalente de um painel fotovoltaico.                                 |

| $C_{FV_P}$ | Parcela da capacitância parasita conectada no terminal positivo do painel fotovoltaico.      |

| $C_{FV_N}$ | Parcela da capacitância parasita conectada no terminal negativo do painel fotovoltaico.      |

| $f_{sw}$   | Frequência de chaveamento.                                                                   |

| $f_o$      | Frequência da tensão da rede elétrica.                                                       |

| $f_{res}$  | Frequência de ressonância do modelo de modo comum.                                           |

| $i_2$      | Corrente do indutor $L_2$ .                                                                  |

| $i_g$      | Corrente injetada na rede elétrica.                                                          |

| $i_{cm}$   | Corrente de fuga                                                                             |

| $i_{cm_2}$ | Parcela da corrente de fuga que circula por $C_{FV_P}$ .                                     |

| $i_{cm_1}$ | Parcela da corrente de fuga que circula por $C_{FV_N}$ .                                     |

| $L_1$      | Indutor do filtro de saída conectado ao terminal <i>A</i> .                                  |

| $L_2$      | Indutor do filtro de saída conectado ao terminal <i>B</i> .                                  |

| $R_g$      | Resistência de conexão ao ponto de aterramento.                                              |

| $r_{L_1}$  | Resistência interna do indutor $L_1$ .                                                       |

| $r_{L_2}$  | Resistência interna do indutor $L_2$ .                                                       |

|               |                                                                            |

|---------------|----------------------------------------------------------------------------|

| $V_{AB}$      | Tensão entre os dois terminais de saída de um inversor monofásico.         |

| $V_{AN}$      | Tensão entre o terminal A do inversor e o terminal negativo do painel.     |

| $V_{AO}$      | Tensão entre o terminal A do inversor e o ponto central do barramento CC.  |

| $V_{BN}$      | Tensão entre o terminal B do inversor e o terminal negativo do painel.     |

| $V_{BO}$      | Tensão entre o terminal B do inversor e o ponto central do barramento CC.  |

| $V_{CM}$      | Tensão de modo comum.                                                      |

| $V_{CC}$      | Tensão do barramento CC.                                                   |

| $V_{E_{CM}}$  | Tensão de modo comum equivalente.                                          |

| $V_{nO}$      | Tensão entre o neutro da rede elétrica e o ponto central do barramento CC. |

| $v_g$         | Tensão monofásica da rede elétrica.                                        |

| $\omega_{ci}$ | Frequência de cruzamento de ganho da malha de controle de corrente.        |

| $\phi_i$      | Margem de fase da malha de controle de corrente.                           |

# Sumário

|            |                                                                 |           |

|------------|-----------------------------------------------------------------|-----------|

| <b>1</b>   | <b>INTRODUÇÃO</b>                                               | <b>27</b> |

| <b>1.1</b> | <b>Motivação</b>                                                | <b>27</b> |

| <b>1.2</b> | <b>Objetivo Geral</b>                                           | <b>29</b> |

| 1.2.1      | Objetivos Específicos                                           | 29        |

| <b>1.3</b> | <b>Contribuições do Trabalho</b>                                | <b>29</b> |

| <b>1.4</b> | <b>Organização do Texto</b>                                     | <b>30</b> |

| <b>1.5</b> | <b>Publicação</b>                                               | <b>30</b> |

| <b>2</b>   | <b>REVISÃO BIBLIOGRÁFICA</b>                                    | <b>33</b> |

| <b>2.1</b> | <b>Capacitâncias Parasitas em Sistemas Fotovoltaicos</b>        | <b>33</b> |

| <b>2.2</b> | <b>Modelo de Modo Comum</b>                                     | <b>34</b> |

| <b>2.3</b> | <b>Requisitos para Sistemas Fotovoltaicos Conectados à Rede</b> | <b>37</b> |

| <b>2.4</b> | <b>Topologias de Inversores Monofásicos sem Transformador</b>   | <b>38</b> |

| 2.4.1      | Inversores de Terra Comum                                       | 38        |

| 2.4.1.1    | Inversor NPC                                                    | 38        |

| 2.4.1.2    | Inversor ANPC                                                   | 40        |

| 2.4.1.2.1  | Inversor Tipo T                                                 | 40        |

| 2.4.2      | Inversores com Desacoplamento do Estado-Zero                    | 41        |

| 2.4.2.1    | Desacoplamento CC                                               | 42        |

| 2.4.2.1.1  | Inversor H5                                                     | 43        |

| 2.4.2.2    | Desacoplamento CA                                               | 44        |

| 2.4.2.2.1  | Inversor HERIC                                                  | 44        |

| 2.4.2.2.2  | Topologia H6 com diodos                                         | 45        |

| 2.4.3      | Topologias de Grampeamento ao Ponto Central                     | 46        |

| 2.4.3.1    | Inversor oH5                                                    | 46        |

| 2.4.3.2    | Inversor H6                                                     | 47        |

| 2.4.3.3    | Inversor PN-NPC                                                 | 48        |

| 2.4.3.4    | Inversores HB-ZVR E HB-ZVR-D                                    | 49        |

| 2.4.3.5    | Inversor HB-ZVSCR                                               | 50        |

| <b>3</b>   | <b>INVERSOR MONOFÁSICO SEM TRANSFORMADOR PROPOSTO</b>           | <b>53</b> |

| <b>3.1</b> | <b>Modelo de Modo Comum para Inversores Monofásicos</b>         | <b>53</b> |

| 3.1.1      | Variação no Indutor de Filtro                                   | 59        |

| 3.1.2      | Variação na Capacitância Parasita                               | 60        |

| <b>3.2</b> | <b>Descrição do Inversor Proposto</b>                           | <b>62</b> |

| 3.2.1      | Modos de Operação                                               | 62        |

|            |                                                                         |            |

|------------|-------------------------------------------------------------------------|------------|

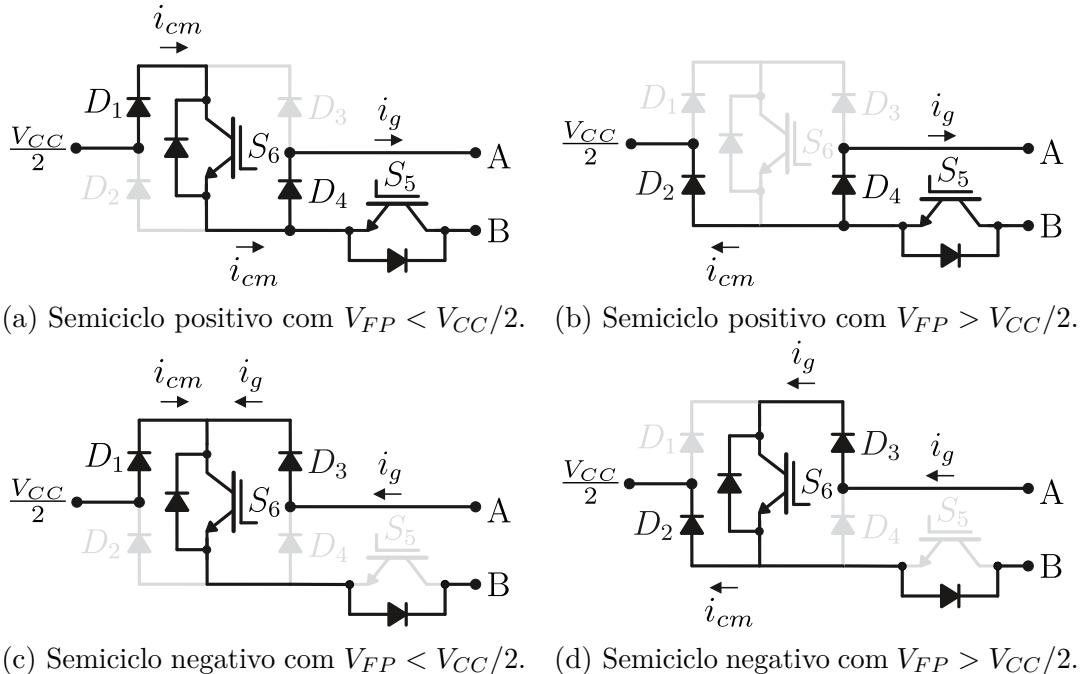

| 3.2.2      | Princípio de funcionamento do ramo de grampeamento . . . . .            | 69         |

| <b>3.3</b> | <b>Descrição da Técnica de Modulação . . . . .</b>                      | <b>70</b>  |

| <b>3.4</b> | <b>Modelagem do Sistema . . . . .</b>                                   | <b>76</b>  |

| 3.4.1      | Modulador PWM . . . . .                                                 | 76         |

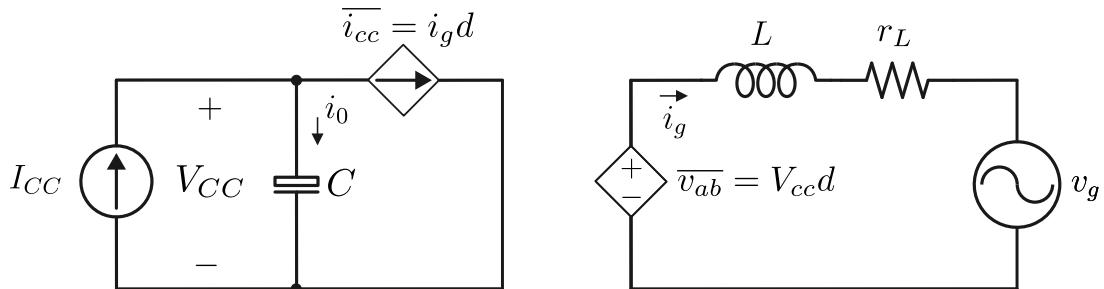

| 3.4.2      | Inversor Monofásico Conectado à Rede . . . . .                          | 78         |

| 3.4.2.1    | Lado CA do Conversor . . . . .                                          | 81         |

| 3.4.2.2    | Lado CC do Conversor . . . . .                                          | 82         |

| <b>3.5</b> | <b>Estratégia de Controle Proposta . . . . .</b>                        | <b>83</b>  |

| 3.5.1      | Controlador Proporcional-Ressonante . . . . .                           | 84         |

| 3.5.2      | Cálculo dos Ganhos . . . . .                                            | 86         |

| <b>4</b>   | <b>ANÁLISE DE RESULTADOS . . . . .</b>                                  | <b>89</b>  |

| <b>4.1</b> | <b>Escolha dos Parâmetros . . . . .</b>                                 | <b>89</b>  |

| <b>4.2</b> | <b>Inversores Propostos na Literatura . . . . .</b>                     | <b>92</b>  |

| 4.2.1      | Inversores com Terra Comum . . . . .                                    | 92         |

| 4.2.2      | Inversores com Desacoplamento CC . . . . .                              | 94         |

| 4.2.3      | Inversores com Desacoplamento CA . . . . .                              | 95         |

| 4.2.4      | Inversores com Grampeamento ao Ponto Central do Barramento CC . . . . . | 96         |

| 4.2.4.1    | Inversor oH5 . . . . .                                                  | 96         |

| 4.2.4.2    | Inversor H6 . . . . .                                                   | 97         |

| 4.2.4.3    | Inversor PN-NPC . . . . .                                               | 98         |

| 4.2.4.4    | Inversor HB-ZVR . . . . .                                               | 98         |

| 4.2.4.5    | Inversor HB-ZVR-D . . . . .                                             | 100        |

| 4.2.4.6    | Inversor HB-ZVSCR . . . . .                                             | 100        |

| <b>4.3</b> | <b>Resultados do Inversor Proposto . . . . .</b>                        | <b>101</b> |

| <b>4.4</b> | <b>Análise das Perdas . . . . .</b>                                     | <b>106</b> |

| 4.4.1      | Perdas nos IGBTs . . . . .                                              | 106        |

| 4.4.1.1    | Perdas por condução . . . . .                                           | 107        |

| 4.4.1.2    | Perdas por chaveamento . . . . .                                        | 108        |

| 4.4.2      | Perdas nos Diodos . . . . .                                             | 109        |

| 4.4.3      | Comparação das Perdas . . . . .                                         | 109        |

| <b>4.5</b> | <b>Resultados Experimentais . . . . .</b>                               | <b>113</b> |

| <b>5</b>   | <b>CONCLUSÕES E TRABALHOS FUTUROS . . . . .</b>                         | <b>117</b> |

| <b>5.1</b> | <b>Conclusões Gerais . . . . .</b>                                      | <b>117</b> |

| <b>5.2</b> | <b>Trabalhos Futuros . . . . .</b>                                      | <b>118</b> |

|            | <b>REFERÊNCIAS . . . . .</b>                                            | <b>119</b> |

# 1 Introdução

## 1.1 Motivação

Durante a pandemia do COVID-19, que desencadeou uma crise energética e o aumento significativo dos preços de energia elétrica, a geração de energia solar fotovoltaica se tornou uma fonte essencial para suprir a demanda energética de vários países ([SOLARPOWER, 2022](#)). Em 2021, a energia solar fotovoltaica obteve um crescimento de 167,8 GW na capacidade instalada, 21% a mais do que os 139,2 GW de 2020, estabelecendo um novo recorde para o setor. Ao mesmo tempo que estes números representam 56% da capacidade instalada de todas as fontes renováveis em 2021, a energia solar fotovoltaica supre apenas 3,7% da demanda de eletricidade mundial com 940 GW de capacidade instalada, enquanto as demais fontes renováveis suprem 24,6% e fontes não-renováveis ainda proveem 71,7% desse total ([SOLARPOWER, 2022](#)). De acordo com [SolarPower \(2022\)](#), a busca dos países por uma matriz elétrica menos dependente de combustíveis fósseis, somada com as preocupações acerca da invasão russa à Ucrânia, irá acelerar o processo de transição para energia solar fotovoltaica, fazendo com que a capacidade instalada globalmente chegue a 2.368 GW em 2026, representando um crescimento expressivo de 151,91% com relação a 2021.

O Brasil mantém sua liderança na América do Sul como o maior mercado de geração solar fotovoltaica com uma capacidade instalada de 22,3 GW ao final de 2022 como apresentada na Figura 1, sendo 31% correspondente à geração centralizada e 69% à geração distribuída. Esse valor, que representa um crescimento de 57,96% e mais de 8 GW de capacidade instalada no ano, corresponde a 10,6% de participação na matriz elétrica brasileira ([ABSOLAR, 2023](#)). De acordo com a Associação Brasileira de Energia Solar Fotovoltaica, mais de R\$ 113,3 bilhões foram investidos e 670,7 mil novos empregos foram gerados no setor fotovoltaico brasileiro desde 2012. O grande crescimento do setor foi impulsionado pela assinatura da lei 14.300/2022 ([BRASIL, 2022](#)), que criou o Marco Legal da Geração Distribuída e garantiu que os projetos já instalados ou cuja solicitação de acesso ocorresse até o dia 07 de janeiro de 2023 se beneficiassem das regras de compensação da Resolução 482 até o final de 2045.

A tendência de descentralização dos sistemas de potência se observa no aumento gradual de capacidade instalada da Geração Distribuída observada na Figura 1. Os sistemas distribuídos reduzem as perdas na transmissão e distribuição de energia, que podem representar até cerca de 30% do custo ao consumidor ([IEA, 2002](#)), visto que os geradores ficam muito próximos ou exatamente na localização do usuário final, como no caso da geração residencial. A geração distribuída por fontes renováveis também oferece

Fig. 1 – Evolução da fonte solar fotovoltaica no Brasil

Fonte: Adaptado de (ABSOLAR, 2023)

benefícios a longo prazo, como a possibilidade de redução do investimento realizado por concessionárias e companhias estatais na construção de plantas de grande porte e na infraestrutura de transmissão (REVESZ; UNEL, 2016). Por contemplar diversas tecnologias e diferentes fontes de energia, a geração distribuída permite a diversificação da matriz energética, diminuindo a dependência do setor em apenas um recurso energético, contribuindo para a robustez da matriz energética nacional (ZILLES et al., 2016).

Nos sistemas de geração distribuída, a função dos inversores é servir como uma *interface* entre duas fontes de energia: o módulo solar e a rede elétrica (ISLAM; MEKHILEF; HASAN, 2015). Os transformadores são utilizados para prover isolamento galvânico entre o gerador fotovoltaico e a rede elétrica, de modo a evitar correntes de fuga e injeção de CC na rede. Entretanto, esses transformadores aumentam o peso e tamanho dos inversores, além de diminuir sua eficiência e a densidade de energia (KHAN et al., 2019).

A retirada dos transformadores desses sistemas tem sido considerada como uma opção viável devido aos benefícios que proporciona, como aumento da eficiência, redução do peso e do tamanho dos inversores. Além disso, os inversores sem transformador podem

ser mais baratos que os sistemas convencionais, tornando a geração fotovoltaica ainda mais competitiva com os sistemas tradicionais de geração de energia (MYRZIK; CALAIS, 2003a). No entanto, esses tipos de inversores apresentam uma grande desvantagem devido à conexão direta entre o arranjo de painéis fotovoltaicos com a rede elétrica sem isolamento galvânico. Como a estrutura metálica dos arranjos fotovoltaicos é aterrada, surgem capacitâncias parasitas entre os terminais dos painéis e o terminal de terra (CHEN; LAI, 2015). Como resultado, uma corrente indesejada flui da rede elétrica para os arranjos fotovoltaicos através do solo e provoca sérios problemas de segurança, distorção na corrente injetada, aumento das perdas e interferências eletromagnéticas. Para lidar com essa questão, os inversores fotovoltaicos sem transformador são desenvolvidos com o objetivo de reduzir a corrente de fuga a valores dentro das normas de segurança estabelecidas e que interfiram ao mínimo na eficiência do sistema.

## 1.2 Objetivo Geral

O objetivo geral do trabalho é o desenvolvimento de uma nova topologia de inversor sem transformador para sistemas fotovoltaicos.

### 1.2.1 Objetivos Específicos

- Realizar uma revisão das principais topologias de inversor sem transformador propostas na literatura;

- Obter o modelo de modo comum que descreva o comportamento da corrente de fuga em relação às tensões presentes no sistema;

- Assegurar que a nova topologia reduza a corrente de fuga e apresente uma boa eficiência quando comparado com as topologias convencionais;

- Realizar simulações das topologias estudadas, a fim de comparar o desempenho da topologia proposta com os inversores sem transformador existentes na literatura;

- Validar experimentalmente o inversor proposto.

## 1.3 Contribuições do Trabalho

Entende-se como as principais contribuições deste trabalho:

- Desenvolvimento de uma nova topologia inversor sem transformador que reduz a corrente de fuga e assegura uma alta eficiência comparado a inversores já existentes na literatura;

- Obtenção de modelo de modo comum que relaciona a corrente de fuga com a tensão da rede elétrica e a com a tensão de modo comum;

- Análise das mudanças no diagrama de Bode de cada parcela da corrente de fuga para variações nos valores da capacitância parasita e indutor do filtro de saída.

## 1.4 Organização do Texto

O restante desse trabalho está organizado da seguinte maneira:

No capítulo 2, inicialmente descreve-se as capacitâncias parasitas intrínsecas aos painéis fotovoltaicos. Em seguida, é apresentado o modelo de modo comum simplificado do inversor fotovoltaico sem transformador conectado à rede. Por fim, realiza-se uma revisão bibliográfica das principais técnicas e topologias de inversores propostos na literatura para redução da corrente de fuga nos sistemas fotovoltaicos.

No capítulo 3, é apresentado um modelo de modo comum detalhado do inversor monofásico sem transformador nos sistemas fotovoltaicos e realiza-se uma análise do comportamento da corrente de fuga em função das variações da tensão de modo comum e na tensão da rede. Em seguida, realiza-se uma análise do comportamento da corrente de fuga em função da variação da capacitância parasita e do indutor de filtro. Após isso, descreve-se a estrutura do conversor proposto, detalhando seus princípios de funcionamento e a modulação utilizada. Por fim, desenvolve-se a modelagem do inversor com o objetivo de controlar a corrente injetada na rede elétrica.

No capítulo 4, são apresentados os resultados de simulação do inversor proposto e das topologias presentes na literatura. Então, são comparadas as performances das topologias simuladas em relação a vários parâmetros, como taxa de distorção harmônica, corrente de fuga, número de dispositivos e tensão sobre as chaves. Realiza-se, então, uma análise das perdas do inversor proposto em comparação a quatro topologias de inversores sem transformador convencionais. Por fim, é detalhada a montagem experimental e apresentados os resultados que validam a nova topologia proposta.

No capítulo 5, realizam-se as conclusões sobre os resultados obtidos, além da sugestão de trabalhos futuros.

## 1.5 Publicação

Durante o desenvolvimento deste projeto, foi elaborado um artigo científico que apresenta o inversor sem transformador de alta eficiência proposto na seção 3. O artigo, intitulado "A Novel Single-Phase Transformerless Grid-Connected PV Inverter", foi publicado no congresso internacional *IEEE Energy Conversion Congress and Exposition (ECCE)*

2022), tendo como autores: Arnaldo O. Cunha Jr, Filipe A. C. Bahia, João P. R. A. Méllo, André P. N. Tahim e Fabiano F. Costa.

## 2 Revisão Bibliográfica

Neste capítulo, é apresentado o modelo concentrado das capacitâncias parasitas em sistemas fotovoltaicos sem transformador, seguido pelo modelo de modo comum frequentemente utilizado em estudos anteriores para o inversor monofásico aplicado a esses sistemas. Por fim, realiza-se uma revisão bibliográfica detalhada para discutir as principais topologias de inversores propostas na literatura com o objetivo de reduzir a corrente de fuga.

### 2.1 Capacitâncias Parasitas em Sistemas Fotovoltaicos

Uma das principais causas dos problemas de segurança em um sistema fotovoltaico sem transformador é a presença das capacitâncias parasitas entre as células dos painéis e o terra, conforme ilustrado na Figura 2. Existem três capacitâncias intrínsecas que podem ser resumidas da seguinte forma (CHEN et al., 2016):

1.  $C_{ce}$ : capacitância entre as células de silício do painel e sua estrutura de alumínio. Embora a área efetiva desse capacitor não seja grande, a distância entre suas placas é muito pequena, tornando seu valor considerável. A capacitância  $C_{ce}$  não depende do tipo de montagem dos módulos, mas sim dos materiais usados em sua confecção.

2.  $C_{cr}$ : Capacitância entre as células de silício e o *rack* de montagem. Seu valor varia com os diferentes tipos de montagem, visto que depende da forma e do tamanho dos *racks* utilizados.

3.  $C_{ct}$ : Capacitância entre as células dos módulos fotovoltaicos e o terra. É considerada o principal parâmetro parasita no sistema fotovoltaico, pois sua área efetiva é bem maior do que as outras capacitâncias. Assim como  $C_{cr}$ , seu valor também varia de acordo com a montagem dos painéis, visto que depende da distância das placas em relação ao solo.

Na Figura 2, é apresentado o modelo concentrado das capacitâncias parasitas em um arranjo de módulos fotovoltaicos. Como o *rack* de montagem e a estrutura de alumínio devem ser aterrados em um sistema fotovoltaico real, considera-se que as três capacitâncias estão em paralelo e a capacitância parasita total  $C_{FV}$  pode ser representada por:

$$C_{FV} = C_{ce} + C_{cr} + C_{ct}. \quad (2.1)$$

Fig. 2 – Modelo concentrado das capacitâncias parasitas em um arranjo de módulos fotovoltaicos.

Fonte: adaptado de [Chen et al. \(2016\)](#).

O valor da capacitância  $C_{FV}$  pode variar entre 50 a 150 nF/kW ([MYRZIK; CALAIS, 2003b](#)) e é diretamente proporcional ao tamanho dos painéis fotovoltaicos. Além disso, depende de diversos outros fatores, como a distância entre as células dos módulos fotovoltaicos, as condições climáticas, a umidade, a presença de partículas sobre os painéis, como areia e sal, entre outros ([CHEN et al., 2016; MA et al., 2015b; LOPEZ et al., 2007; SU; SUN; LIN, 2011; XIAO; XIE, 2010a](#)). A presença da capacitância parásita pode estabelecer um caminho direto entre a rede elétrica e os painéis fotovoltaicos caso não haja isolamento galvânico oferecido pelo transformador, ocasionando uma corrente de fuga através da terra que traz problemas de segurança, interferência eletromagnética e distorção na corrente injetada na rede. O comportamento dessa corrente e os diferentes modos de reduzi-la são analisados a seguir.

## 2.2 Modelo de Modo Comum

A fim de realizar uma análise inicial do comportamento da corrente de fuga, a Figura 3 apresenta o modelo de um sistema fotovoltaico sem transformador que utiliza um inversor em ponte completa para converter a corrente CC em corrente CA a ser injetada na rede elétrica. Na entrada do sistema, um arranjo de painéis fotovoltaicos, representados por Fotovoltaico (FV), são conectados ao capacitor  $C_1$ , denominado de capacitor do barramento CC. O barramento CC é ligado ao inversor, que por sua vez é conectado à rede elétrica através de um filtro L composto de dois indutores  $L_1$  e  $L_2$ , respectivamente conectados em cada um dos terminais de saída do inversor, denominados de A e B. A capacitância parásita  $C_{FV}$  é representada por um capacitor conectado ao

terminal negativo do arranjo de painéis fotovoltaicos, indicado como o ponto  $N$ . Através dessa capacitância, uma corrente parasita  $i_{cm}$  circula pelo solo devido aos aterramentos realizados na estrutura dos painéis fotovoltaicos e da rede elétrica.

Fig. 3 – Modelo geral de um inversor fotovoltaico sem transformador.

Fonte: adaptado de [Freddy et al. \(2014a\)](#).

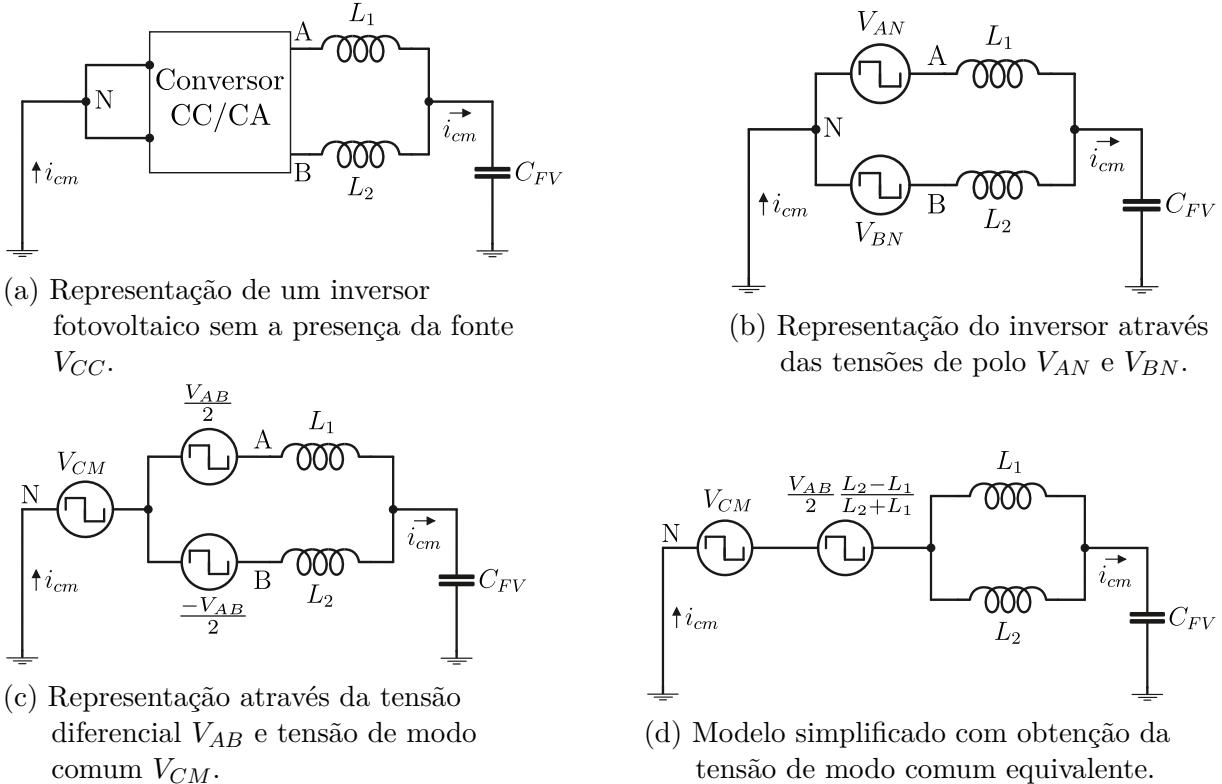

A conexão entre a rede elétrica e os painéis fotovoltaicos realizada pela capacitância parasita origina um circuito de modo comum ressonante com o filtro de saída, o conversor e a rede elétrica. Uma tensão de modo comum alterna, que depende principalmente da topologia, modulação e do esquema de controle utilizados, pode alimentar esse circuito ressonante e originar altos valores de corrente de fuga. Com o objetivo de compreender a natureza da tensão sobre a capacitância  $C_{FV}$ , os modelos representados na Figura 4 são utilizados.

A Figura 4a representa o sistema sem a presença da tensão  $V_{CC}$ , uma vez que o circuito está sendo analisado no domínio CA e o capacitor se comporta como um circuito aberto para tensões contínuas. Para fins de análise, o terminal  $N$  da fonte CC é adotado como ponto de referência. Com base nisso, as diferenças de potencial entre os terminais de saída do inversor e a referência  $N$  podem ser denominadas de tensões de polo do circuito, sendo identificadas como  $V_{AN}$  e  $V_{BN}$ . A Figura 4b apresenta o inversor fotovoltaico como duas fontes de tensão que representam suas tensões de polo.

A tensão diferencial de saída do conversor  $V_{AB}$  é determinada pela diferença entre as tensões  $V_{AN}$  e  $V_{BN}$ . Por outro lado, a tensão de modo comum  $V_{CM}$  é obtida através da média aritmética das tensões  $V_{AN}$  e  $V_{BN}$ , como apresentado nas equações a seguir:

$$V_{AB} = V_{AN} - V_{BN} \quad (2.2)$$

Fig. 4 – Modelo de modo comum de um inversor fotovoltaico sem transformador.

Fonte: adaptado de [Freddy et al. \(2014a\)](#).

$$V_{CM} = \frac{V_{AN} + V_{BN}}{2} \quad (2.3)$$

Utilizando as equações (3.1) e (3.2), é possível expressar as tensões de polo  $V_{AN}$  e  $V_{BN}$  em termos das tensões  $V_{AB}$  e  $V_{CM}$ , como demonstrado em (2.4) e (2.5):

$$V_{AN} = V_{CM} + \frac{V_{AB}}{2} \quad (2.4)$$

$$V_{BN} = V_{CM} - \frac{V_{AB}}{2} \quad (2.5)$$

A Figura 4c representa o sistema ao substituir as tensões de polo pelos valores obtidos em (2.4) e (2.5). Em estudos como o de [Gonzalez et al. \(2008\)](#), esse circuito é simplificado para o modelo apresentado na Figura 4d. Nesse caso, a tensão de modo comum equivalente  $V_{E_{CM}}$  é descrita por:

$$V_{E_{CM}} = V_{CM} + \frac{V_{AB}}{2} \frac{L_2 - L_1}{L_1 + L_2} \quad (2.6)$$

Ao analisar a equação (2.6), nota-se que a contribuição da tensão diferencial no modelo de modo comum do inversor fotovoltaico sem transformador é proporcional à

diferença entre os valores dos indutores em cada braço da saída do inversor ( $L_1$  e  $L_2$ ). Logo, caso os dois indutores tenham o mesmo valor, essa contribuição é anulada (GONZALEZ et al., 2008).

Neste caso, a corrente de fuga  $i_{cm}$  está fortemente correlacionada com o comportamento da tensão de modo comum  $V_{CM}$ . Essa tensão, por sua vez, é influenciada pela topologia de inversor utilizada no sistema. Isso ocorre pois a tensão de modo comum é determinada pela média aritmética das tensões de polo  $V_{AN}$  e  $V_{BN}$ , que variam a cada modo de operação do inversor. A variação da tensão  $V_{CM}$  faz com que as capacitâncias parasitas do sistema sejam constantemente carregadas e descarregadas. Essa situação provoca a ocorrência de altos valores de corrente de fuga.

Como mencionado anteriormente, a reatância capacitiva tende ao infinito para tensões contínuas. Com base nisso, pode-se concluir que uma maneira de mitigar a corrente de fuga nos sistemas sem transformador é garantir que  $V_{CM}$  permaneça constante durante todo o período de funcionamento do inversor. Ao fazer isso, é possível atender os requisitos estabelecidos pelas normas para a circulação das correntes de fuga nesses sistemas.

## 2.3 Requisitos para Sistemas Fotovoltaicos Conectados à Rede

Os sistemas fotovoltaicos devem cumprir alguns requisitos que são regulamentados por normas internacionais e nacionais. Internacionalmente, a norma IEC 62109-2 (COMMISSION, 2011) determina requisitos de segurança para os inversores nesses sistemas e serve como base para normas de vários países. No Brasil, a norma NBR 16690 (Associação Brasileira de Normas Técnicas (ABNT), 2018) determina os requisitos de projeto para instalações elétricas de arranjos fotovoltaicos, enquanto a NBR 16149 (Associação Brasileira de Normas Técnicas (ABNT), 2013) determina características da interface de conexão com a rede elétrica de distribuição.

Essas normas estabelecem diversas métricas para a operação adequada do sistema fotovoltaico. Entre as principais métricas estão a distorção harmônica total, ou *total harmonic distortion* (THD) em inglês, os níveis de harmônicas na corrente injetada na rede, o nível da corrente CC injetada, a corrente de fuga, a faixa de operação da tensão e frequência da rede, o fator de potência (FP), além de requisitos para detecção de ilhamento, critérios para aterramento, reconexão e sincronização automática do sistema.

Em relação à corrente de fuga, também denominada de corrente residual, tanto a norma internacional IEC 62109-2 como a norma brasileira NBR 16690 determinam um valor máximo de 300 mA rms para uma Unidade de Condicionamento de Potência (UCP) de até 30 kVA. Caso a corrente exceda esse valor, o sistema de supervisão de corrente residual deve causar interrupção em até 0,3 s. Além disso, a UCP deve ser desligada de qualquer circuito de saída referenciado ao terra (a rede elétrica, por exemplo) dentro de

0,5 s caso ocorra um aumento repentino de 100 mA rms nas correntes residuais.

## 2.4 Topologias de Inversores Monofásicos sem Transformador

A fim de solucionar os problemas causados pela ausência dos transformadores, as topologias de inversores sem transformador para sistemas fotovoltaicos utilizam diferentes técnicas para mitigar a corrente parasita que circula nesses sistemas. Baseado na técnica utilizada, esses inversores podem ser divididos em três grandes classes:

1. Inversores com terra comum;

2. Inversores com desacoplamento do estado-zero;

3. Inversores com grampeamento ao ponto central.

As topologias com terra comum possuem uma conexão galvânica entre o neutro da rede elétrica e um ponto de referência do barramento **CC**. Essa configuração garante que a tensão sobre a capacitância parasita se mantenha constante durante toda a operação do inversor, evitando assim a ocorrência de altos valores de corrente de fuga. As topologias de desacoplamento do estado-zero permitem o desacoplamento dos módulos fotovoltaicos da rede elétrica durante os modos de roda-livre do inversor. Esses modos de operação ocorrem quando a corrente não flui da fonte *CC* para a rede, mas sim circula entre a rede elétrica e as chaves do inversor. Já as topologias de grampeamento ao ponto central não apenas desacoplam, mas também grampeiam o circuito de roda-livre ao ponto central do barramento **CC**. Nesta seção, são apresentadas as topologias mais comuns propostas na literatura, destacando suas características, vantagens, limitações e aplicações.

### 2.4.1 Inversores de Terra Comum

As topologias com terra comum são caracterizadas por uma ligação galvânica entre o neutro da rede elétrica e a referência da fonte **CC**. Com essa ligação, a tensão sobre as capacitâncias parasitas do sistema se mantém constante durante todo o período de funcionamento do inversor e a corrente de fuga é aproximadamente zero.

#### 2.4.1.1 Inversor NPC

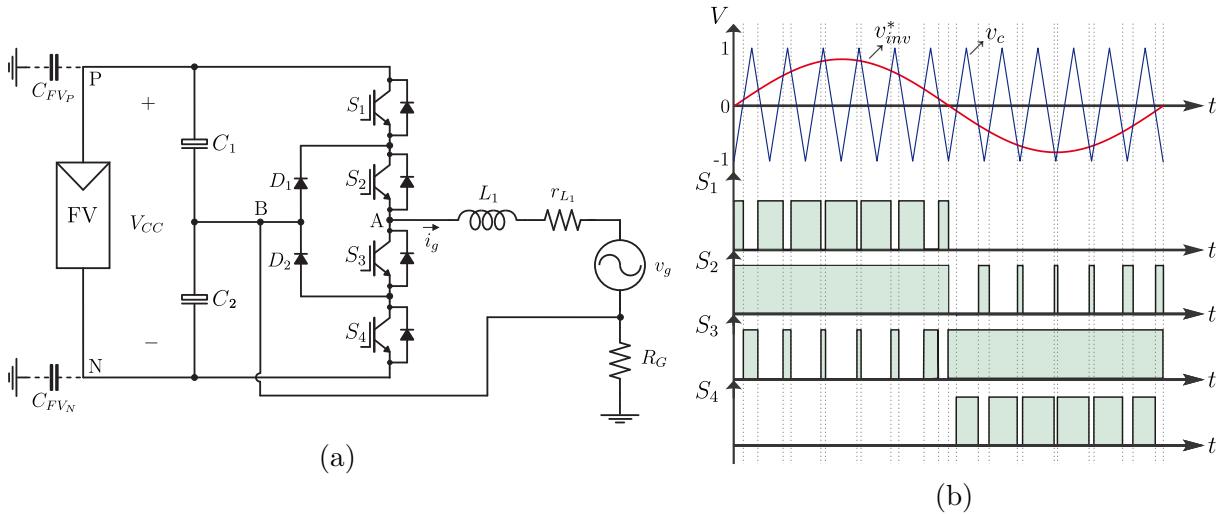

A fim de melhorar a eficiência e reduzir o *ripple* da corrente de saída do inversor em meia-ponte, a topologia denominada de *Neutral Point Clamped* (**NPC**) foi proposta por Baker em uma patente na década de 70 e primeiramente mencionada em um artigo por [Nabae, Takahashi e Akagi \(1981\)](#). Este inversor foi de grande importância para a

Fig. 5 – Estrutura (a) e pulsos de chaveamento (b) do inversor NPC.

Fonte: adaptado de [Nabae, Takahashi e Akagi \(1981\)](#).

época pela redução do tamanho e custo do filtro ao produzir uma tensão de saída de três níveis ([MA et al., 2015a; CALAIS; AGELIDIS, 1998](#)).

A versão monofásica em meia-ponte do inversor NPC é apresentada na Figura 5a, enquanto os pulsos de chaveamento são exibidos na Figura 5b. Durante o modo ativo do semiciclo positivo da tensão de referência, as chaves \$S\_1\$ e \$S\_2\$ são acionadas e a corrente \$i\_g\$ flui através delas para a rede elétrica. A tensão de saída entre os dois terminais de saída do inversor (\$V\_{AB}\$) é estabelecida em \$\frac{V\_{CC}}{2}\$. Já durante o modo ativo do semiciclo negativo da tensão de referência, \$S\_3\$ e \$S\_4\$ são acionadas e a corrente flui da rede elétrica para o ponto central do barramento CC por meio dessa chaves. Nesse período, a tensão aplicada na saída é de \$-\frac{V\_{CC}}{2}\$. Durante os períodos de roda-livre, as chaves \$S\_2\$ e \$S\_3\$ são acionadas em ambos os semiciclos da tensão de referência. Durante esses modos, a tensão \$V\_{AB}\$ é estabelecida em zero, os dispositivos \$D\_1\$ e \$S\_2\$ conduzem caso a corrente \$i\_g\$ seja positiva, enquanto \$S\_3\$ e \$D\_2\$ conduzem caso \$i\_g\$ seja negativa.

Como o ponto de aterramento da rede elétrica está sempre conectada ao ponto central do barramento CC, a tensão sobre as capacitâncias parasitas nesse sistema são mantidas fixas, o que reduz a corrente de fuga a aproximadamente zero. No entanto, esta topologia possui duas principais desvantagens: a primeira é que, por ser uma topologia em meia-ponte, a tensão do barramento CC precisa ser o dobro do que em topologias baseadas no inversor em ponte-completa. Além disso, o inversor NPC possui uma distribuição desigual das perdas nas chaves, o que requer o superdimensionamento dos dispositivos semi-condutores utilizados em cerca de 30% a 50% acima de sua corrente nominal ([BRUCKNER; BERNET; GULDNER, 2005a](#)).

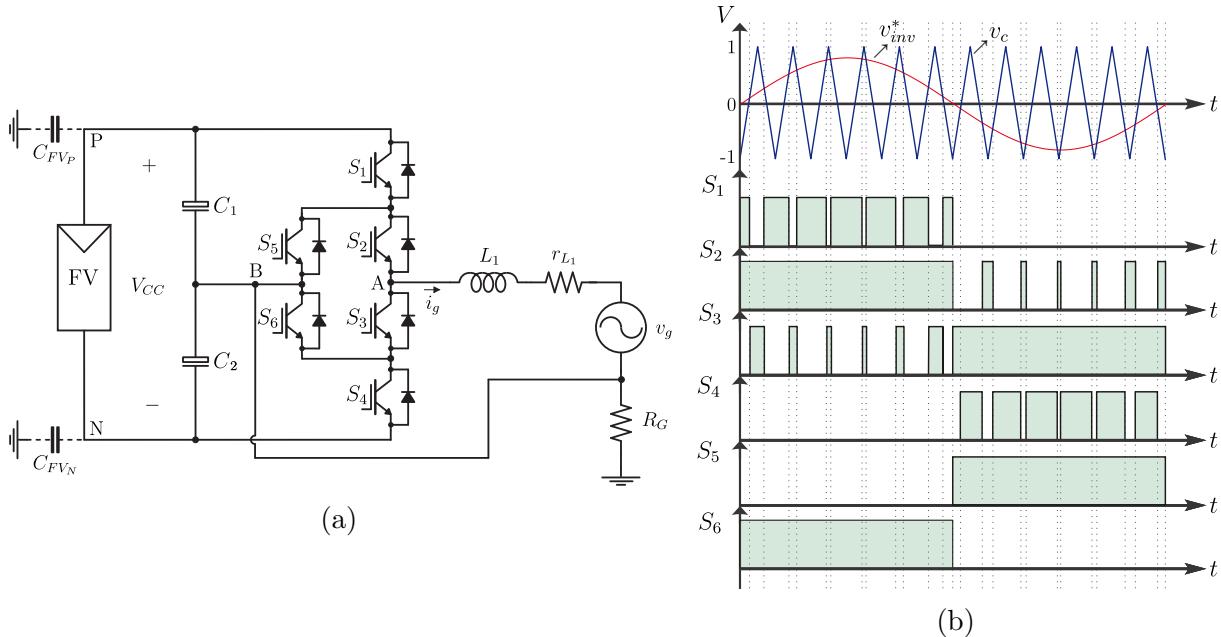

### 2.4.1.2 Inversor ANPC

Para solucionar os problemas de distribuição irregular de perdas, Bruckner, Bernet e Guldner (2005a) propuseram um inversor, denominado de *Active Neutral Point Clamped* (ANPC), que substitui os diodos  $D_1$  e  $D_2$  da topologia NPC pelas chaves  $S_5$  e  $S_6$ . Com essa alteração, o grampeamento ao ponto central pode ser realizado pelo caminho superior, formado pelas chaves  $S_2$  e  $S_5$ , ou pelo caminho inferior, formado pelas chaves  $S_3$  e  $S_6$  (MA et al., 2009; MA et al., 2009). A estrutura do conversor e os pulsos de chaveamento são apresentados na Figura 6. As chaves  $S_1$  a  $S_4$  são acionadas da mesma forma que no inversor NPC. A chave  $S_6$  é acionada durante o semiciclo positivo da tensão de referência, garantindo que  $i_g$  percorra o caminho inferior do ramo de grampeamento nos dois sentidos da corrente. No semiciclo negativo da tensão de referência,  $S_5$  é acionada de forma a garantir que  $i_g$  percorra o caminho superior do ramo de grampeamento em ambos os sentidos da corrente. Essa possibilidade de grampeamento nos dois sentidos da corrente permite o controle das perdas de condução e de chaveamento do inversor. Os estados redundantes de chaveamento são escolhidos de forma a garantir a distribuição uniforme das perdas, elevando a eficiência do conversor (RODRIGUEZ et al., 2010; BRUCKNER; BERNET; GULDNER, 2005b). Com a adoção dessa topologia, o superdimensionamento dos dispositivos semicondutores é reduzido, já que a distribuição das perdas é equilibrada.

Fig. 6 – Estrutura (a) e pulsos de chaveamento (b) do inversor ANPC.

Fonte: adaptado de Bruckner, Bernet e Guldner (2005a).

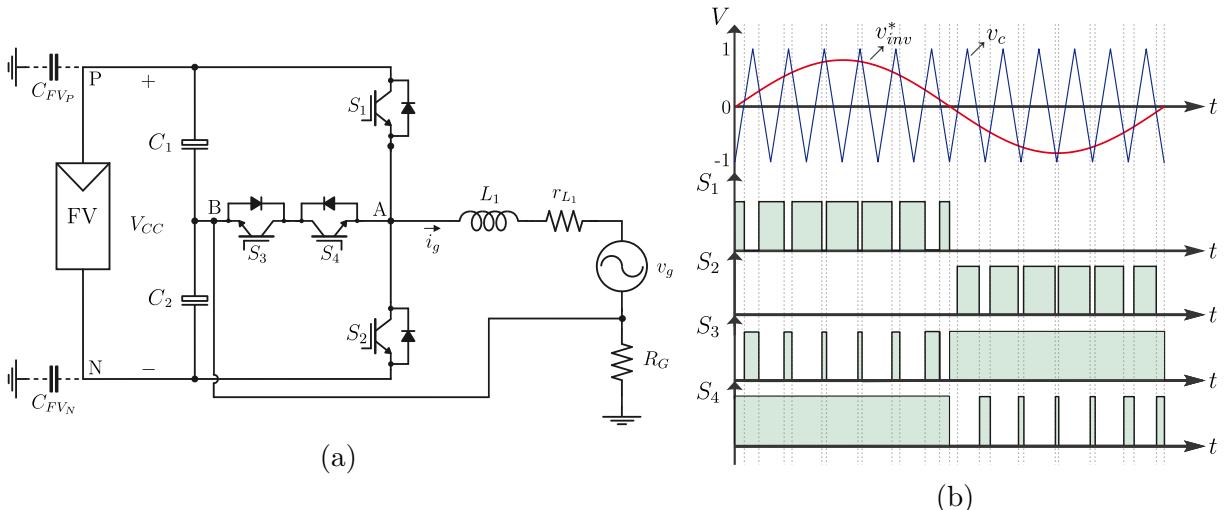

### 2.4.1.2.1 Inversor Tipo T

A fim de reduzir as perdas por chaveamento e diminuir o número de chaves em comparação às topologias em meia-ponte mencionadas anteriormente, foi proposto o

inversor apresentado na Figura 7a. Esta topologia, patenteada pela empresa alemã Conergy (KNAUP, 2009) e mais tarde denominada de inversor tipo T (SCHWEIZER; FRIEDLI; KOLAR, 2013; MA et al., 2009), utiliza duas chaves para conectar uma das saídas do inversor meia-ponte ao ponto central do barramento CC, que por sua vez está ligado ao neutro da rede elétrica.

O comportamento desse inversor pode ser observado na Figura 7b, onde são apresentados os sinais de *gate* das suas chaves. Durante o semiciclo positivo, a chave  $S_4$  permanece sempre ativa, enquanto  $S_1$  e  $S_3$  comutam complementarmente na frequência de chaveamento, permitindo que a corrente flua ora através de  $S_1$ , ora através de  $S_4$  e do diodo em anti-paralelo a  $S_3$ . Durante o semiciclo negativo,  $S_3$  permanece ativa, enquanto as chaves  $S_2$  e  $S_4$  comutam complementarmente, de modo que a corrente  $i_g$  flui ora através de  $S_2$ , ora através de  $S_3$  e do diodo em anti-paralelo a  $S_4$ . Com essa estratégia, além de diminuir a quantidade de chaves do inversor, o número de dispositivos no caminho da corrente é reduzido em relação às topologias NPC e ANPC. Como consequência, as perdas por condução são reduzidas, proporcionando maior eficiência ao sistema.

Fig. 7 – Estrutura (a) e pulsos de chaveamento (b) do inversor Tipo T.

Fonte: adaptado de Knaup (2009).

Os inversores NPC, ANPC e tipo T são muito utilizados em conversores multinível para elevar a qualidade de energia e reduzir a complexidade das aplicações de alta potência (CHEN; HOTCHKISS; BAZZI, 2018; SAMADAEI et al., 2018; MEHTA; KUMAR, 2018). São úteis também para obter uma alta eficiência com baixas perdas de chaveamento (BISWAS; KUMAR; MAITY, 2018; NOOR et al., 2013).

#### 2.4.2 Inversores com Desacoplamento do Estado-Zero

A topologia de inversor em ponte completa, ilustrada na Figura 3, apresenta diversas vantagens para aplicação em sistemas fotovoltaicos, como sua estrutura simples, que resulta

em menor custo e maior eficiência. Além disso, sua utilização permite uma tensão de barramento CC menor em comparação com o inversor em meia-ponte, o que possibilita a utilização de capacitores de barramento menos robustos e uma menor quantidade de módulos fotovoltaicos em série. A operação desse inversor com Modulação por Largura de Pulso Senoidal Bipolar, do inglês *Bipolar Senoidal Pulse Width Modulation (SPWM)*, resulta em uma tensão diferencial de dois níveis na saída do inversor e uma tensão de modo comum aproximadamente constante. Visto que a corrente de fuga  $i_{cm}$  depende fortemente da tensão de modo comum, conforme apresentado na seção 2.2, as correntes residuais do inversor em ponte completa com SPWM bipolar são reduzidas. Entretanto, devido ao número limitado de níveis, a tensão de saída possui um *ripple* elevado, o que aumenta o tamanho do filtro e, consequentemente, reduz a eficiência do sistema.

Para aumentar o número de níveis e reduzir o tamanho do filtro, uma opção é operar o inversor em ponte completa com modulação SPWM unipolar, que resulta em três níveis de tensão na saída. No entanto, esse modo de operação introduz variações de alta frequência na tensão de modo comum, sobretudo na frequência de chaveamento. Para gerar os três níveis de saída, é necessário acionar o modo de operação que resulta em uma tensão nula, chamado de estado-zero, que é ativado ligando as duas chaves superiores ou inferiores do circuito. Esse modo também é conhecido como período de roda-livre, pois a corrente da rede elétrica flui entre as chaves do inversor sem passar pela fonte CC. Os estados ativos e estados-zero são acionados em todos os períodos de chaveamento, resultando em variações de alta frequência na tensão de modo comum.

Nos sistemas fotovoltaicos sem transformador, as variações de alta frequência na tensão de modo comum são altamente indesejáveis, visto que resultam na circulação das correntes de fuga. Uma abordagem para reduzir essas variações e mitigar a corrente de fuga consiste em desacoplar a rede elétrica dos painéis fotovoltaicos durante os períodos de estado-zero. Nesta subseção, são apresentadas as principais topologias presentes na literatura que utilizam essa técnica.

#### 2.4.2.1 Desacoplamento CC

No desacoplamento CC, chaves são acrescentadas ao lado CC do inversor em ponte completa com a finalidade de desativá-las nos períodos de roda-livre, de forma a isolar os módulos fotovoltaicos da rede elétrica durante esses estados. Essa técnica pode ajudar a reduzir a circulação da corrente de fuga, mas ela não é completamente eliminada devido às capacitâncias de junção das chaves, que podem gerar pequenas variações na tensão de modo comum e ainda servir como caminho para essa corrente indesejada (YANG et al., 2012). A principal desvantagem do desacoplamento CC é que as chaves adicionadas para isolar a ponte-H da fonte CC passam a integrar o caminho da corrente durante os estados ativos, aumentando as perdas por condução.

### 2.4.2.1.1 Inversor H5

O inversor H5, proposto por Victor et al. (2008), é apresentado na figura 8a. Desenvolvida pela SMA Solar Technology, uma das maiores produtoras de inversores fotovoltaicos do mundo, essa topologia é composta por um inversor em ponte completa com uma chave adicional ( $S_5$ ) que realiza o desacoplamento CC do inversor durante o período de roda-livre, operando na frequência de chaveamento  $f_{sw}$ . Enquanto as chaves superiores  $S_1$  e  $S_3$  operam na frequência da rede elétrica, as chaves inferiores  $S_2$  e  $S_4$  comutam na frequência  $f_{sw}$ .

Fig. 8 – Estrutura (a) e pulsos de chaveamento (b) do inversor H5.

Fonte: adaptado de Victor et al. (2008).

O diagrama de pulsos de chaveamento deste conversor é apresentado na Figura 8b. Uma modulação SPWM unipolar é utilizada para obter uma saída de tensão de três níveis no inversor. Durante os modos ativos, o transistor  $S_5$  permanece ativo, enquanto as chaves  $S_1$  a  $S_4$  operam da mesma forma que no inversor em ponte completa, com  $S_1$  e  $S_4$  sendo acionadas no semiciclo positivo da tensão de referência, enquanto  $S_2$  e  $S_3$  são ligadas no semiciclo negativo. Já durante os estados-zero, a chave  $S_5$  é aberta para desacoplar a fonte CC da rede elétrica, permitindo que a corrente flua através da chave bidirecional formada pelos transistores  $S_1$  e  $S_3$ . Com isso,  $i_g$  flui através da chave  $S_1$  e do diodo em anti-paralelo de  $S_3$  caso a corrente esteja no sentido positivo, enquanto flui por  $S_3$  e pelo diodo em anti-paralelo de  $S_1$  no sentido negativo da corrente. A maior desvantagem desse inversor, como já explicado anteriormente, é que a chave  $S_5$ , utilizada para realizar o desacoplamento CC, sempre se encontra no caminho da corrente durante os modos ativos, o que aumenta as perdas por condução e reduz a eficiência.

### 2.4.2.2 Desacoplamento CA

A técnica de desacoplamento em CA consiste em adicionar chaves no lado CA do inversor para isolar a rede elétrica dos painéis fotovoltaicos durante os períodos de estado-zero. Embora esta técnica permita uma redução da corrente de fuga, a tensão de modo comum não é mantida constante durante todo o funcionamento do inversor, assim como ocorre nas topologias com desacoplamento CC. Isso acontece pois o ramo de roda-livre flutua em relação ao barramento CC durante os modos de estado-zero. Nesta seção, serão apresentados dois inversores que utilizam o desacoplamento CA para mitigar a corrente de fuga nos sistemas fotovoltaicos.

#### 2.4.2.2.1 Inversor HERIC

A topologia, denominada de *Highly Efficient and Reliable Inverter Concept* (HERIC), foi proposta em (SCHMIDT; SIEDLE; KETTERER, 2003). Desenvolvida em 2003 pela fabricante de inversores alemã Sunway's Solar Inverter, foi amplamente utilizada em vários conversores comerciais (ARAUJO; ZACHARIAS; MALLWITZ, 2010; BURGER; KRANZER, 2009). Nesta topologia, apresentada na Figura 9a, o desacoplamento CA é realizado por uma chave bidirecional formada por  $S_5$  e  $S_6$ . Durante os períodos de roda-livre, a corrente flui apenas por uma das chaves e do diodo em anti-paralelo da outra, o que torna esse conversor uma alternativa de alta eficiência para redução da corrente de fuga.

Fig. 9 – Estrutura (a) e pulsos de chaveamento (b) do inversor HERIC.

Fonte: adaptado de Schmidt, Siedle e Ketterer (2003).

A modulação SPWM aplicada a este inversor é ilustrada na Figura 9b. No semiciclo positivo, as chaves  $S_1$  e  $S_4$  são acionadas durante o modo ativo e a corrente flui através delas, enquanto as chaves  $S_5$  e  $S_6$  são ativas nos períodos de roda-livre e a corrente flui por  $S_5$  e pelo diodo em anti-paralelo de  $S_6$ . Durante o semiciclo negativo, a corrente flui através de  $S_2$  e  $S_3$  que estão ativas durante o modo ativo, enquanto que  $S_6$  e o diodo em anti-paralelo de  $S_5$  conduzem no período de roda-livre. No momento em que é realizado o

desacoplamento, a tensão de modo comum oscila, pois a saída do inversor está flutuando em relação ao barramento CC e não há controle sobre as tensões de polo nesse momento. De toda forma, a corrente de fuga é reduzida (KEREKES et al., 2011; PAULINO; MENEGÁZ; SIMONETTI, 2011) e a eficiência do inversor é mantida elevada, visto que apenas dois dispositivos semicondutores conduzem em todos os períodos de chaveamento (KEREKES, 2009).

#### 2.4.2.2.2 Topologia H6 com diodos

Foi proposto em (JI; WANG; ZHAO, 2013) outro inversor que utiliza o desacoplamento CA para reduzir a corrente de fuga. Nessa topologia, apresentada na Figura 10a, quatro transistores atuam como chaves de um inversor de ponte completa, enquanto duas chaves e dois diodos extras são adicionados para servir como caminho da corrente durante os estados de tensão zero.

Fig. 10 – Estrutura (a) e pulsos de chaveamento (b) do inversor H6 com diodos.

Fonte: adaptado de Ji, Wang e Zhao (2013).

Os pulsos de chaveamento desse inversor são apresentados na Figura 10b. Durante o modo de condução do semiciclo positivo, as chaves  $S_1$ ,  $S_4$  e  $S_5$  são acionadas e a corrente injetada na rede flui através delas, enquanto que no estado de roda-livre apenas a chave  $S_5$  continua ativa e a corrente percorre  $D_2$  e  $S_5$ . No modo ativo do semiciclo negativo, as chaves  $S_2$ ,  $S_3$  e  $S_6$  são acionadas e conduzem  $i_g$ , enquanto que durante o período de roda-livre apenas a chave  $S_6$  permanece acionada, servindo de caminho da corrente junto ao diodo  $D_1$ . A grande desvantagem dessa topologia é que a corrente nos modos ativos do inversor sempre passam por três transistores, aumentando assim as perdas por condução.

### 2.4.3 Topologias de Grampeamento ao Ponto Central

Como discutido ao longo da subseção 2.4.2, o desacoplamento de estado-zero não garante a eliminação da corrente de fuga. Isso acontece pois, em inversores que utilizam esta técnica, as tensões de polo  $V_{AN}$  e  $V_{BN}$  flutuam em relação ao barramento CC durante os períodos de roda-livre. Dessa forma, a tensão de modo comum, dada pela média aritmética das duas tensões de polo, passa a ser determinada pela interação das capacitâncias de junção das chaves com os circuitos ressonantes presentes no circuito. Isso resulta em variações da tensão de modo comum e, consequentemente, em uma corrente de fuga que fluirá pelo sistema. Para solucionar este problema, foram desenvolvidas tecnologias que conectam o caminho da corrente durante os períodos de roda-livre ao ponto central do barramento CC. Com isso, consegue-se fixar a tensão de modo comum em metade da tensão da fonte CC e, dessa forma, mitigar a corrente de fuga (ZHANG et al., 2013a; XIAO; XIE, 2010b; XIAO et al., 2011). Esta subseção apresenta algumas das principais topologias de inversores que aplicam esta técnica.

#### 2.4.3.1 Inversor oH5

A topologia proposta em Xiao et al. (2011) foi desenvolvida com base no inversor H5, discutido na seção 2.4.2.1.1. Além da chave extra existente no H5 que realiza o desacoplamento CC, a topologia denominada de *Optimized H5* (oH5) e apresentada na Figura 11a possui mais uma chave adicionada ao lado CC do inversor em ponte completa, que tem como objetivo realizar o grampeamento ao ponto central do barramento CC, composto por um divisor de tensão capacitivo.

Fig. 11 – Estrutura (a) e pulsos de chaveamento (b) do inversor oH5.

Fonte: adaptado de Xiao et al. (2011).

A modulação aplicada nesta topologia é apresentada na Figura 11b. A chave  $S_5$  é sempre ativa nos modos de condução do inversor em ambos os semiciclos. Durante esses modos, a corrente flui pelas chaves  $S_5$ ,  $S_1$  e  $S_4$  no semiciclo positivo e pelas chaves  $S_5$ ,  $S_2$  e  $S_3$  no semiciclo negativo. A chave extra  $S_6$  opera de maneira complementar a  $S_5$ , sendo acionada nos períodos de roda-livre do inversor. Nesses períodos, a corrente sempre flui através da chave bidirecional formada por  $S_1$  e  $S_3$ . No semiciclo positivo, a chave  $S_1$  e o diodo em anti-paralelo de  $S_3$  conduzem  $i_g$ , enquanto no semiciclo negativo a corrente flui através de  $S_3$  e pelo diodo em anti-paralelo de  $S_1$ .

O grampeamento ao ponto central do barramento CC realizado pela chave  $S_6$  garante que a tensão de modo comum se mantenha constante durante todos os períodos de roda-livre. Caso o potencial do laço de roda-livre, do inglês *freewheeling path voltage* ( $V_{FP}$ ), seja menor do que metade da tensão do barramento CC, o diodo em anti-paralelo de  $S_6$  é diretamente polarizado e passa a conduzir uma pequena corrente até que a tensão do laço se iguale a  $\frac{V_{CC}}{2}$ . Caso  $V_{FP}$  seja maior do que  $\frac{V_{CC}}{2}$ , a chave  $S_6$  conduzirá a corrente até que se iguale ao valor desejado, fazendo com que a tensão de modo comum se mantenha fixa em  $\frac{V_{CC}}{2}$  e a corrente de fuga seja reduzida.

A fim de prevenir o curto-círcito no capacitor  $C_1$  do barramento CC, um tempo de espera, denominado de tempo morto, é acrescentado entre os sinais de disparo das chaves  $S_5$  e  $S_6$ . Contudo, durante o tempo morto, a tensão de modo comum oscila, levando ao aumento da corrente de fuga nesse período. Além disso, essa topologia apresenta a desvantagem característica dos inversores com desacoplamento CC, que é um aumento nas perdas por condução devido à presença da chave de desacoplamento  $S_5$  no caminho da corrente durante os modos ativos do inversor.

#### 2.4.3.2 Inversor H6

Gonzalez et al. (2007) propôs uma nova topologia ao adicionar duas chaves de desacoplamento CC e um ramo de grampeamento ao inversor em ponte completa. Esta topologia, ilustrada na Figura 12a, apresenta um ramo de grampeamento com um divisor de tensão capacitivo e dois diodos com o objetivo de fixar a tensão de modo comum na metade da tensão do barramento CC durante todo o período de funcionamento do inversor.

Os pulsos de disparo do inversor são apresentados na Figura 12b. Durante o semiciclo positivo, as chaves  $S_1$  e  $S_4$  estão sempre ativas e as chaves  $S_5$  e  $S_6$  comutam na frequência de chaveamento com os mesmos sinais de disparo e de maneira complementar a  $S_2$  e  $S_3$ . No modo ativo do inversor, que produz uma tensão de saída  $V_{AB} = \frac{V_{CC}}{2}$ , as chaves  $S_1$ ,  $S_4$ ,  $S_5$  e  $S_6$  funcionam como caminho da corrente injetada na rede. No período de roda-livre,  $S_2$  e  $S_3$  são acionadas e a corrente se divide por dois caminhos:  $S_1$  e o diodo em anti-paralelo de  $S_3$  e por  $S_4$  e o diodo em anti-paralelo de  $S_2$ . No semiciclo negativo,  $S_2$  e  $S_3$  estão sempre acionadas e as chaves  $S_1$  e  $S_4$  comutam complementarmente a  $S_5$

Fig. 12 – Estrutura (a) e pulsos de chaveamento (b) do inversor H6.

Fonte: adaptado de [Gonzalez et al. \(2007\)](#).

e  $S_6$ . Durante o modo ativo, a corrente flui através de  $S_2$ ,  $S_3$ ,  $S_5$  e  $S_6$ , enquanto que no modo de roda-livre se divide em dois caminhos:  $S_3$  e o diodo em anti-paralelo de  $S_1$  e por  $S_2$  e o diodo em anti-paralelo de  $S_4$ .